계면 편집기

1. 개요

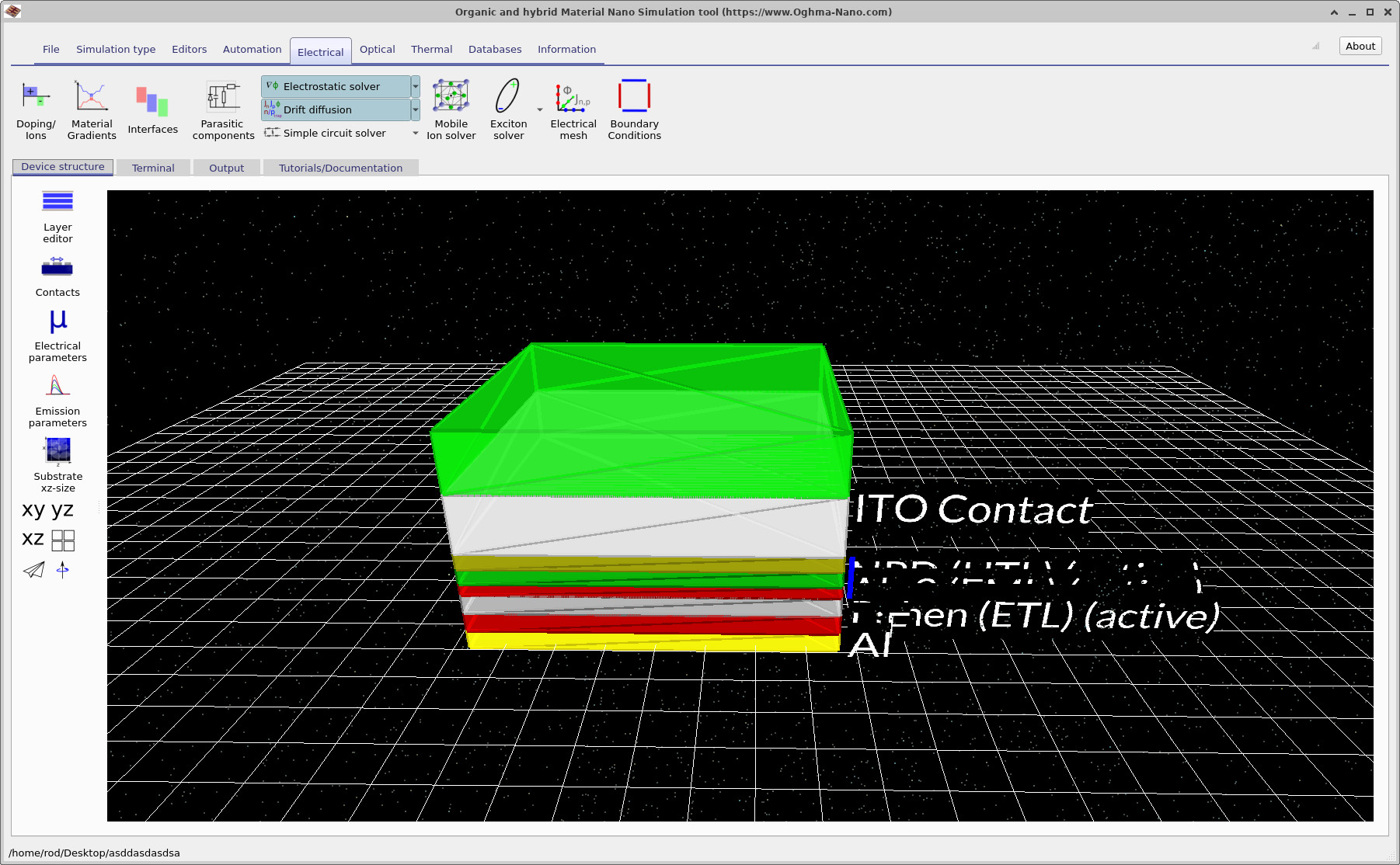

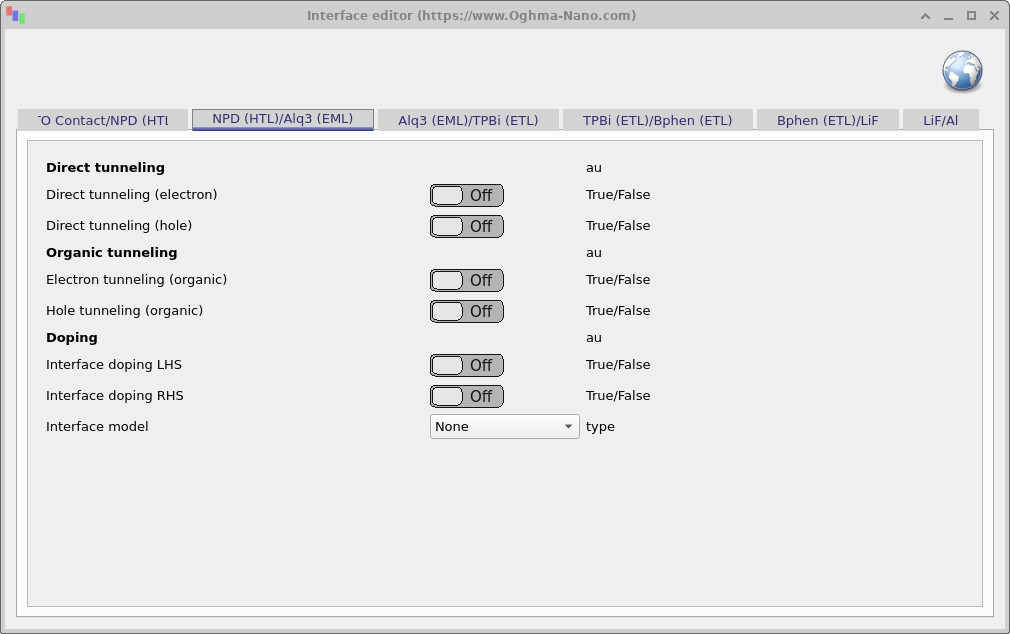

계면 편집기는 재료 경계에서 발생하는 전자 수송 현상을 제어합니다. 계면은 장치 구조에서 인접한 각 레이어 쌍에 대해 자동으로 나열됩니다. 기본적으로 전하 운반자는 전도대 또는 가전자대의 구배에 따라 계면을 가로질러 drift 및 diffusion할 수 있습니다: 에너지에서 오르막으로 이동하는 운반자는 장벽을 만나 더 어렵게 넘어가고, 반면 내리막으로 이동하는 운반자는 쉽게 통과합니다. 계면 편집기는 이러한 기본 drift–diffusion 모델에 추가 수송 메커니즘을 도입하여, 예를 들어 원래는 어려운 오르막 전이를 도울 수 있도록 합니다. Electrical 리본에서 Interfaces 아이콘(빨강, 초록, 파랑 막대)을 클릭하여 편집기를 여십시오.

2. 파라미터

- 직접 터널링 (전자 / 정공) — 운반자의 직접 양자 터널링을 계면 장벽을 통해 활성화합니다. 이론 섹션에 설명된 모델에 기반합니다: \[ J = A(n-n^{eq})V \exp\left(-B\sqrt{\phi}\right), \] 여기서 \(A\)의 단위는 m·s\(^{-1}\)·V\(^{-1}\), \(B\)는 무차원(피팅 파라미터), \(\phi\)는 장벽 높이, \(V\)는 인가 바이어스, \(d\)는 계면 두께입니다. 전자와 정공에 대해 각각 별도의 토글이 있으며, 각자 고유한 A/B 값을 가집니다.

- 유기 터널링 — 유기 헤테로접합에서 적용되는 특수한 경우로, 여기서 운반자는 계면에 국소화된 트랩 상태로 drift합니다. 이론 섹션에 설명된 바와 같이, 터널링 전류는 다음과 같이 표현됩니다: \[ J_p = q T_{h}\left((p_{1}-p_{1}^{eq})-(p_{0}-p_{0}^{eq})\right), \] 정공의 경우, 그리고 \[ J_n = -q T_{e}\left((n_{1}-n_{1}^{eq})-(n_{0}-n_{0}^{eq})\right), \] 전자의 경우이며, 여기서 \(T_h\)와 \(T_e\)는 편집기 토글을 통해 설정되는 속도 상수입니다.

- 계면 도핑 (LHS/RHS) — 한 메쉬 포인트 두께의 전하 시트를 계면의 왼쪽(LHS) 또는 오른쪽(RHS)에 적용합니다. 값은 양수 또는 음수가 될 수 있어 계면 전하 축적 또는 공핍을 시뮬레이션할 수 있습니다. 이는 경계에서의 포획 전하 또는 OFET에서의 문턱 전압 이동을 모델링하는 데 유용합니다.

3. 시뮬레이션에서의 적용

계면 과정은 전류 수송과 장치 특성에 강한 영향을 미칩니다:

- 터널링은 장벽이 얇거나 트랩 보조 hopping이 유기–유기 계면에서 가능할 때 지배적입니다.

- 계면 도핑은 대전된 결함층 또는 의도적인 계면 엔지니어링을 모사하며, 국소 밴드 밴딩과 주입 장벽을 수정합니다.

이러한 메커니즘을 결합함으로써 계면 편집기는 유기 및 하이브리드 헤테로구조에서의 현실적인 장치 물리를 포착할 수 있게 해주며, OLED의 트랩 보조 터널링부터 OFET의 계면 전하 효과까지 다룰 수 있습니다.