NMOS コンデンサチュートリアル (パート B): バンドベンディング、電荷、表面電位

1. イントロダクション

パート A では、2D NMOS コンデンサシミュレーションの設定と実行に焦点を当てました。

このセクションでは、ソルバ出力の物理的解釈へと進みます。

以下に示すすべての図は、シミュレーション出力の snapshots ディレクトリから生成されており、

異なる印加ゲート電圧に対応しています。

全体を通して念頭に置くべき重要な考え方は、NMOS コンデンサは 静電気学によって支配されるということです。印加されたゲート電圧はシリコン内部の電荷を再分布させ、 それによってエネルギーバンドが曲がり、Si/SiO2 界面における表面電位が定まります。

2. 静電ポテンシャルと表面電位

まず、静電ポテンシャル

(phi.csv) を調べることから解析を始めます。これはポアソン方程式によって解かれる基本量です。

ポテンシャルは、印加されたゲート電圧が

SiO2 酸化膜とシリコンの間でどのように分配されるかを直接示し、したがってその後のすべてのバンドベンディングを制御する

静電境界条件を定めます。

NMOS コンデンサでは、印加電圧は構造全体に一様には降下しません。 代わりに、酸化膜とシリコンの間の電圧分配は、 それらの相対誘電率と厚さによって支配されます。 より低い誘電率を持つ酸化膜では、薄い領域に強い電場が生じます。 一方、シリコンはバイアスに依存する広がりを持つ空間電荷領域を形成して応答します。 これらの効果は静電ポテンシャルプロファイルに直接現れます。

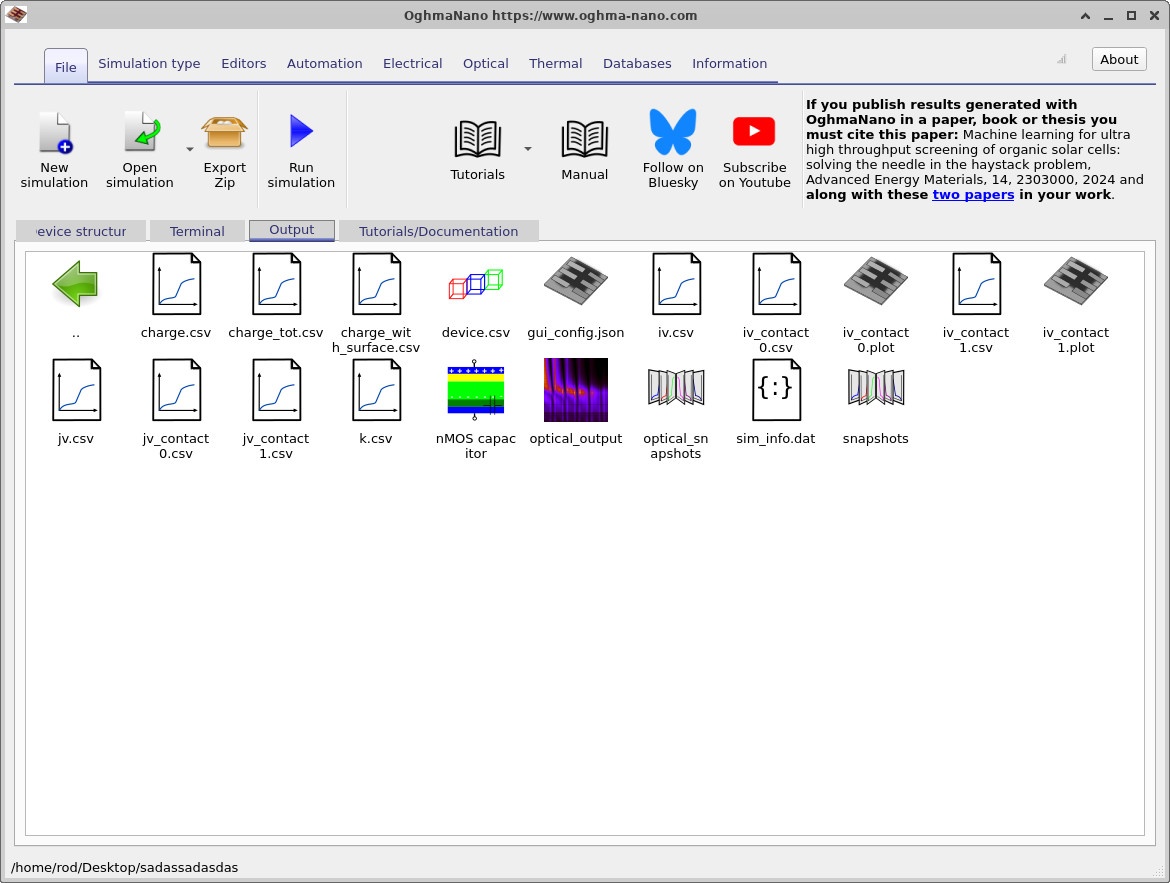

静電ポテンシャルは、snapshots 出力を用いて可視化されます。

シミュレーション終了後、Output タブに切り替え

(?? を参照)、

snapshots ディレクトリをダブルクリックして snapshots ウィンドウを開いてください。

snapshots ウィンドウ内で、青いプラスアイコンをクリックしてプロット項目を追加し、

その後 File to plot 列のドロップダウンメニューを使用して

phi.csv を選択します。

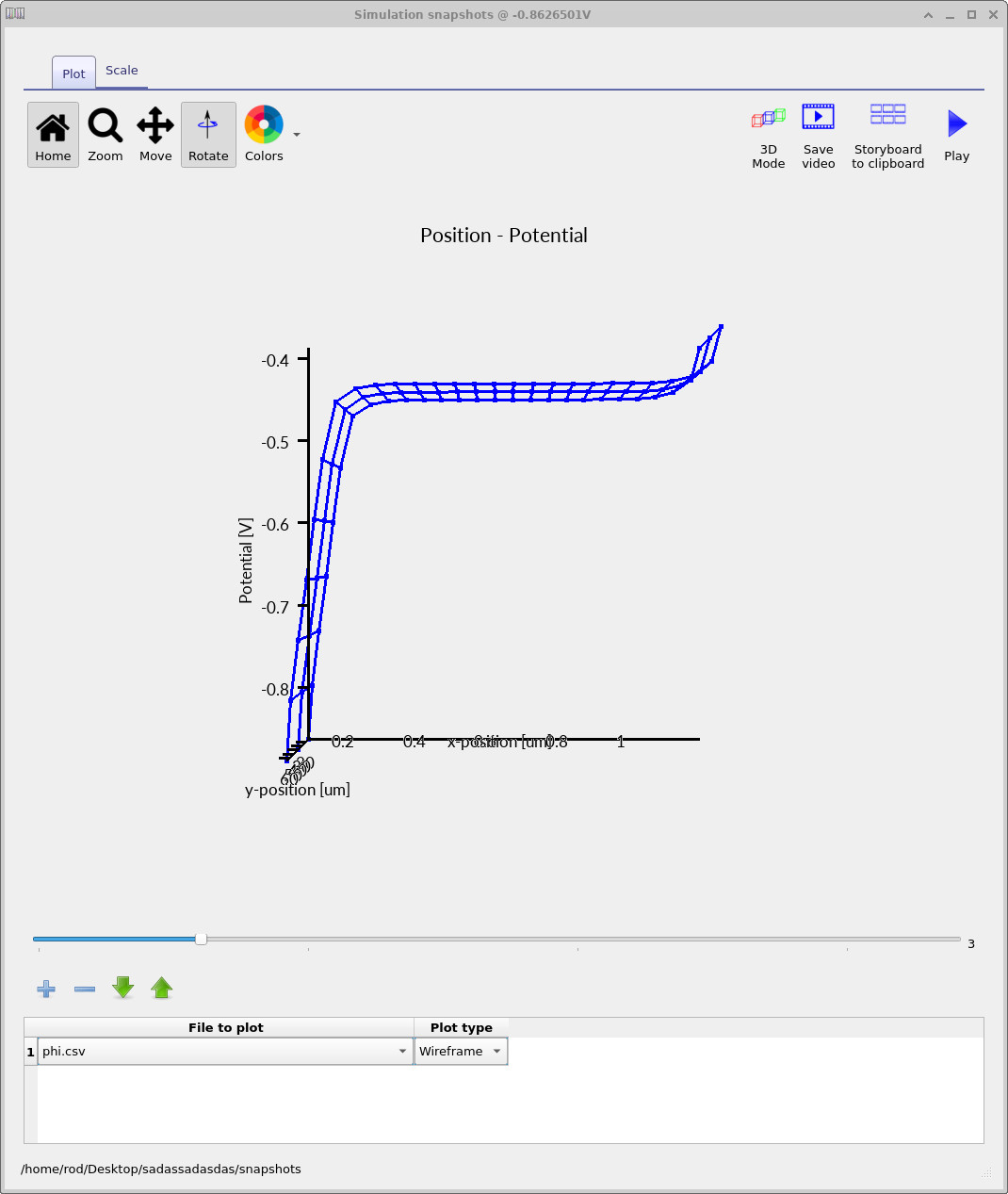

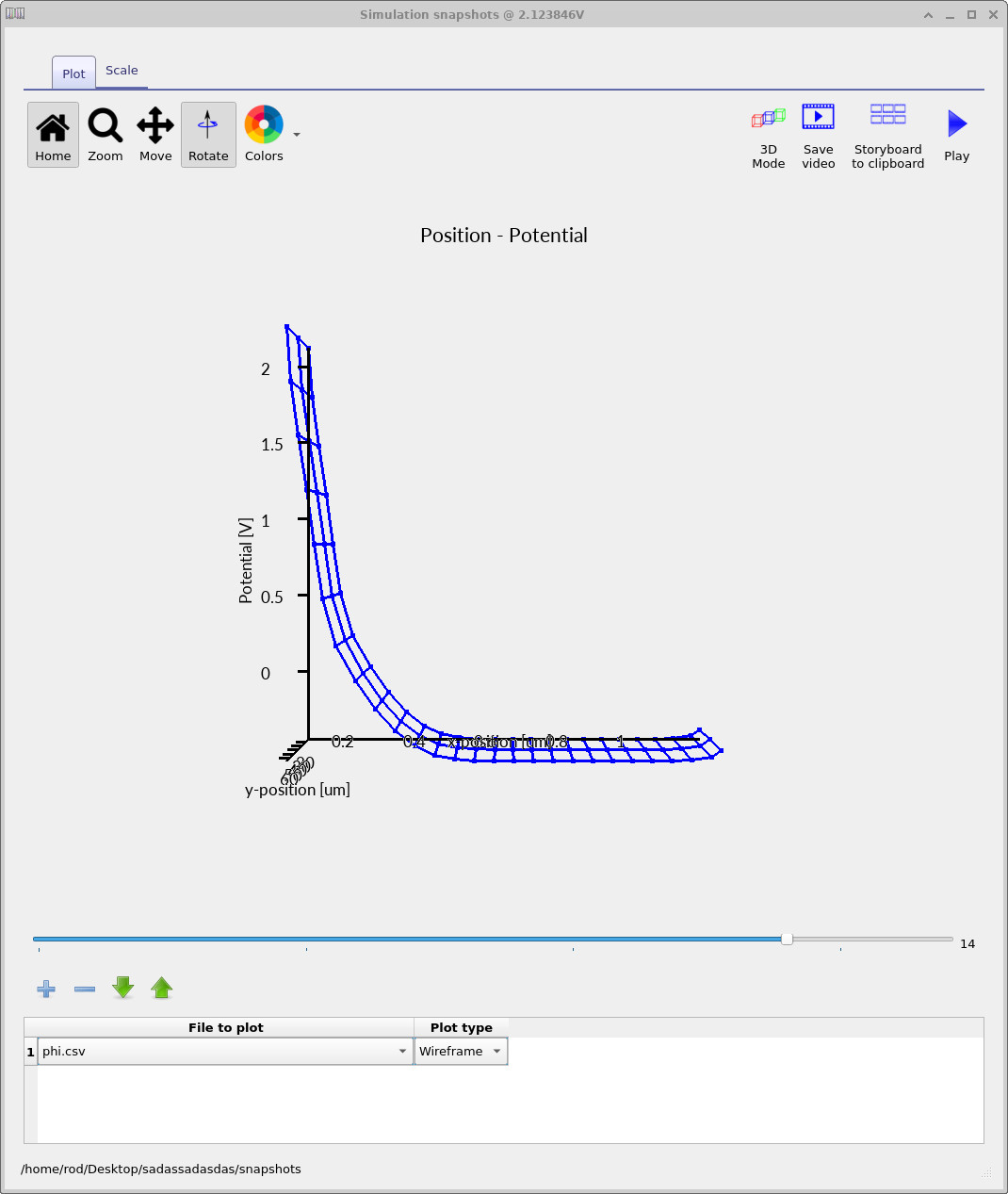

各サーフェスは、バイアス掃引における異なるゲート電圧での静電ポテンシャルに対応します。

スライダバーを使うことで、電圧を順にたどりながら、

印加ゲートバイアスの関数としてポテンシャルがどのように変化するかを調べることができます。

snapshots ディレクトリを

ダブルクリックすると、静電ポテンシャルやエネルギーバンドなどの

内部シミュレーション変数にアクセスできます。

負のゲートバイアスでは、ポテンシャルは酸化膜を横切って急激に変化しますが、 バルクシリコン中ではほぼ一定のままです。 これは、p 型シリコンが印加電場を遮蔽するために容易に電荷を再配置でき、 基板深部には弱い電場しか残らないことを示しています。一方、ゲート電圧が正になると、 シリコンはもはや電場を完全には遮蔽できなくなります。 Si/SiO2 界面近傍に顕著なポテンシャル勾配が発達し、 ゲートバイアスとともに幅が増加する空乏領域が定義されます。 この表面電位が、エネルギーバンドの曲がり方を決定する鍵となる量です。

次のセクションでは、伝導帯端と価電子帯端を調べます。 これらのバンドプロファイルは新しい物理を導入するものではなく、 ここで解析した静電ポテンシャル分布の直接の結果です。

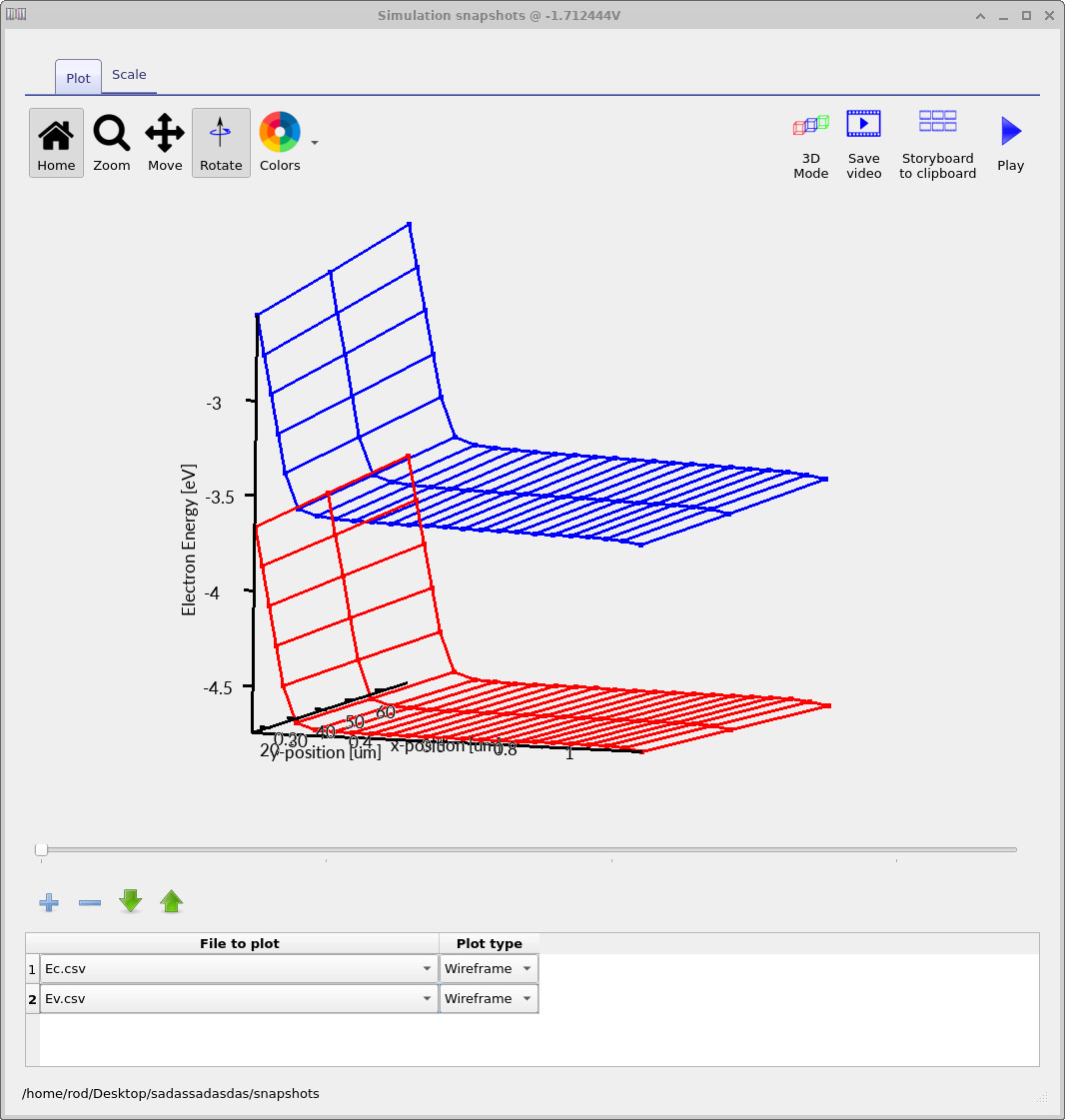

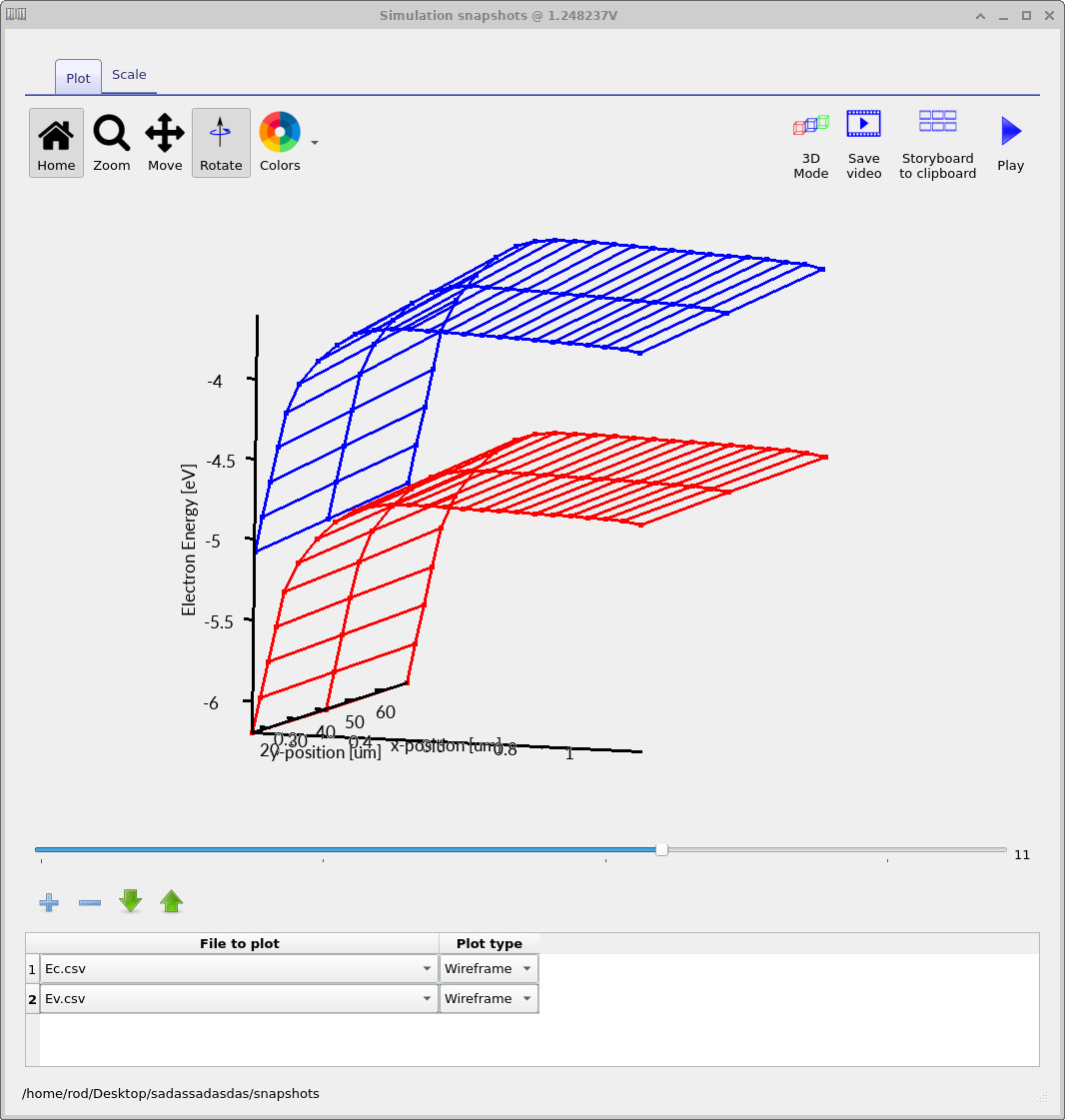

3. 伝導帯および価電子帯のバンドベンディング

ここでは、異なる印加ゲート電圧に対する位置の関数として、

伝導帯 (Ec.csv) と価電子帯 (Ev.csv) を調べます。

これらを一緒にプロットすると、

シリコン内のバンドベンディングを直接可視化できます。これは、

前節で解析した静電ポテンシャルの直接的な結果です。

プロットを解釈する前に、バンド端がどのように定義されているかを思い出しておくと有用です。

ここで用いている drift–diffusion 定式化では、伝導帯および価電子帯のエネルギーは

静電ポテンシャル phi と次のように関係付けられます。

Ec(x) = −χ − q φ(x)

および

Ev(x) = −χ − Eg − q φ(x)

ここで、χ は電子親和力、Eg はバンドギャップ、

φ(x) は静電ポテンシャルです。

両方のバンド端は phi に線形に依存するため、

静電ポテンシャルの空間変化は、伝導帯および価電子帯の曲がりとして直接現れます。

バンド端は snapshots 出力を使って可視化されます。

前と同様に Output タブから snapshots viewer を開き、その後

青いプラスアイコンを 2 回クリックして 2 つのプロット項目を追加します。

最初の項目には Ec.csv を、2 番目の項目には Ev.csv を選択してください。

これにより、伝導帯端と価電子帯端を、位置と印加ゲート電圧の関数として

3 次元的に一緒に表示できます。

負のゲートバイアスでは、伝導帯と価電子帯の両方が Si/SiO2 界面近傍で上向きに曲がります。 バンド端は静電ポテンシャルに従うため、この上向きの曲がりは、 バルクに対する表面電位の増加を反映しています。 バンドプロファイルだけからも、表面領域が 正孔に富む静電構成へと駆動されていることが分かります。

ゲート電圧が正になると、バンドは 界面近傍で下向きに曲がります。 この曲率の変化は、表面電位の低下と シリコン内の空乏領域形成を示しています。 この段階では、NMOS コンデンサは静電的に空乏化されていますが、まだ反転には至っていません。 この結論に達するためにキャリア密度についての仮定は必要ありません。バンドベンディング自体が、 基礎となる静電気学を直接コード化しています。

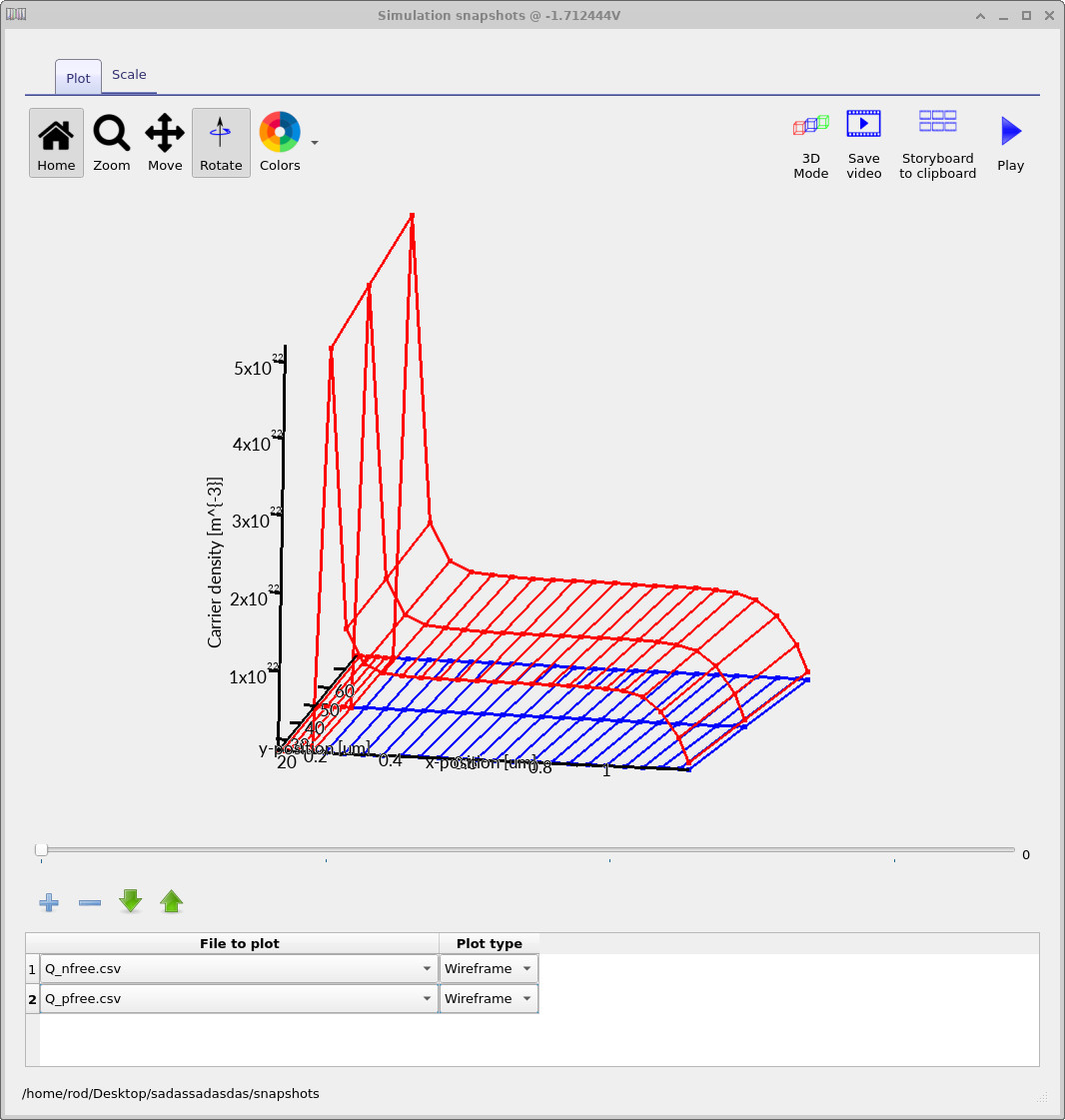

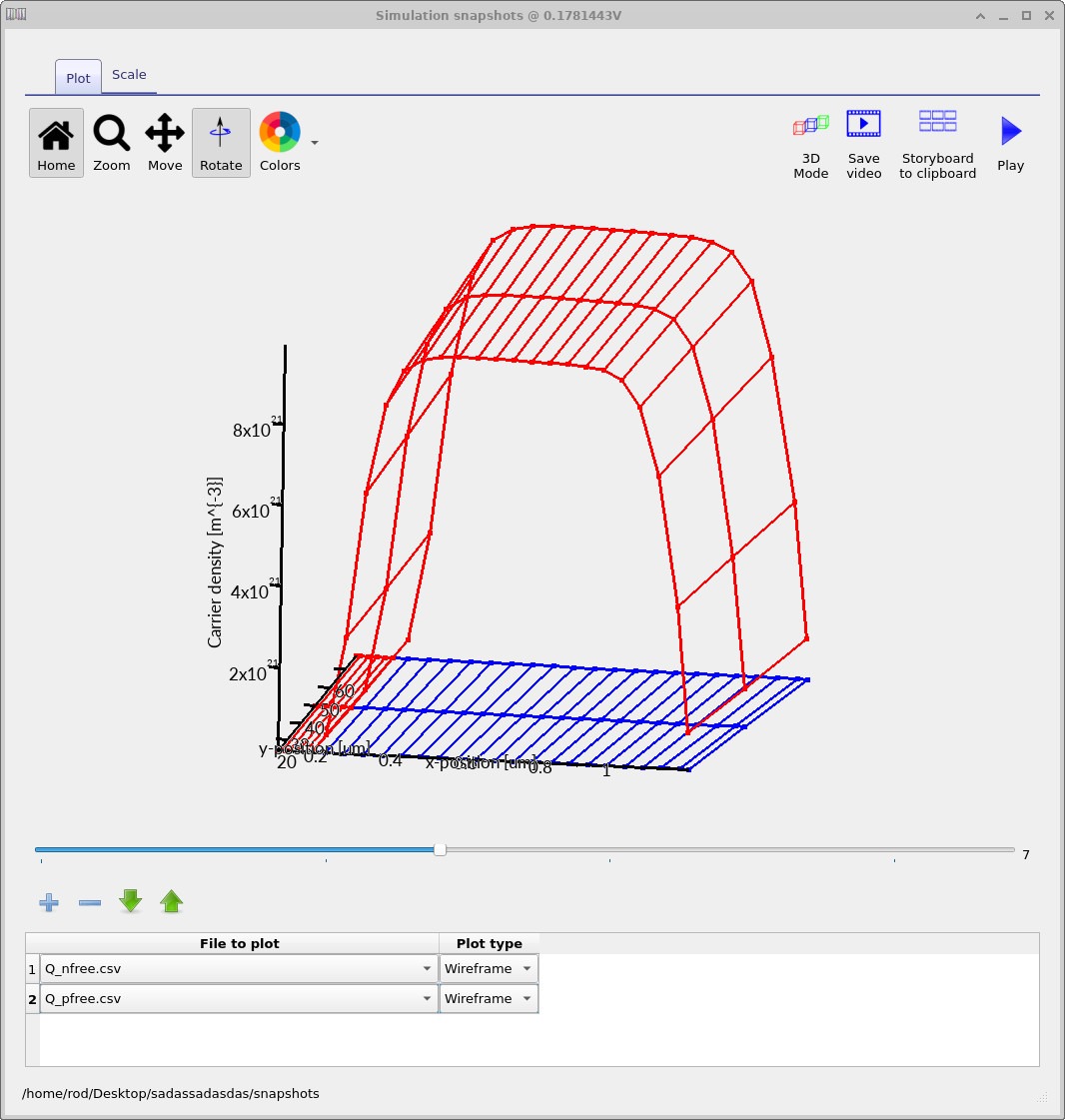

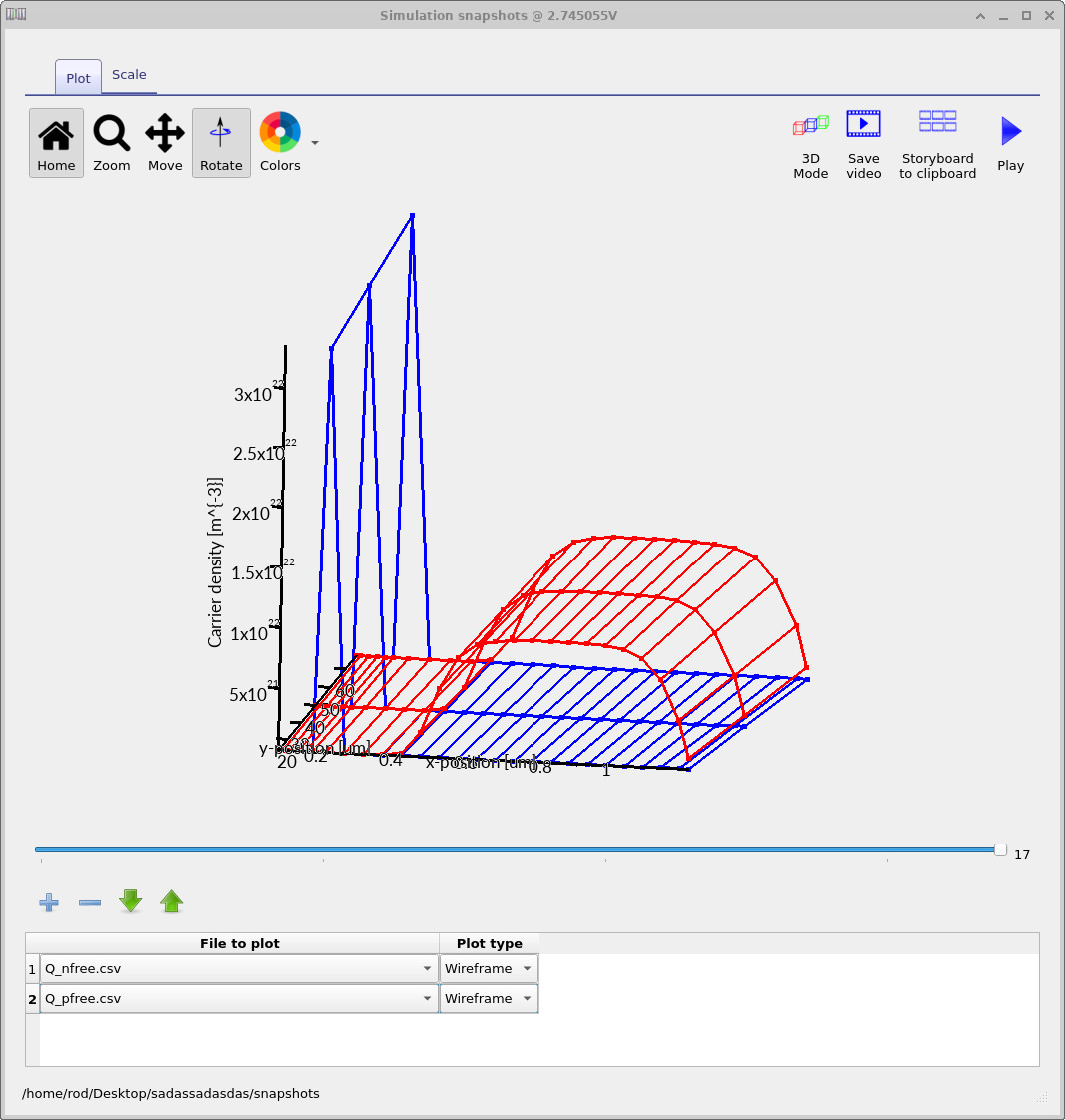

4. 自由キャリア密度

次に、シリコン中の自由キャリア密度を調べることによって、

NMOS コンデンサの静電応答を明示的に見ていきます。

図 ??–

??

には、代表的なゲート電圧において snapshots 出力から抽出した

正孔密度 (Q_pfree.csv) と電子密度 (Q_nfree.csv) が示されています。snapshots viewer では、色の割り当ては純粋にプロット順で決まります。

最初に追加した量は 青 で描画され、

2 番目は 赤 で描画されます。

ここに示す図では、電子 (Q_nfree.csv) を最初にプロットしているため

青で表示され、正孔 (Q_pfree.csv) は 2 番目にプロットしているため赤で表示されています。

これらのファイルを逆の順序で追加すると、色も逆になります。

負のゲートバイアスでは (図 ??)、 赤いサーフェスが正孔密度に対応します。 Si/SiO2 界面で鋭い増加が見られ、これは正孔の静電的 蓄積を示しています。 青いサーフェス(電子密度)はシリコン全体で無視できるほど小さく、 負バイアス下の p 型基板と整合的です。ゲートバイアスがゼロへ向かって増加すると (図 ??)、 界面近傍の赤いサーフェスの大きさは低下します。 正孔は表面から押しのけられ、移動電荷が減少した領域が形成されます。 これは空乏の始まりを示しており、空間電荷は次第に 自由キャリアではなく固定されたイオン化アクセプタによって支配されるようになります。

正のゲートバイアスの下では (図 ??)、 正孔密度(赤)は界面近傍で強く抑制され、明確な空乏領域が形成されます。 電子密度(青)はこのバイアス範囲全体でなお低いままであり、デバイスが まだ強い反転に入っていないことを示しています。

これらのキャリア密度プロットを総合すると、 先にポテンシャルおよびバンド端図から推測した静電的描像を 直接かつ定量的に確認できます。 すなわち、シリコン中の移動電荷の再分布によって 蓄積と空乏がどのように生じるかを明示的に示しています。 電子が表面電荷を支配する強い反転への遷移は、 後続のチュートリアルに委ねます。

5. フェルミ準位とバンド占有

ここでは、伝導帯 (Ec.csv)、価電子帯 (Ev.csv)、

電子および正孔の準フェルミ準位 (Fn.csv および Fp.csv) を

snapshots 出力からプロットすることで、

エネルギーバンドとキャリア統計を一緒に見ていきます。

これらの量を合わせることで、NMOS コンデンサの静電気学だけでなく、

バイアス下でキャリアが利用可能な状態をどのように占有するかも記述できます。

??

に示すプロットを再現するには、

Output タブを開き、snapshots ディレクトリをダブルクリックし、

青いプラスアイコンを使って 4 つのプロット項目を追加します。順に次を選択してください:

Fn.csv— 電子準フェルミ準位Fp.csv— 正孔準フェルミ準位Ec.csv— 伝導帯端Ev.csv— 価電子帯端

snapshots viewer はプロット順に基づいて色を割り当てます: 最初の量は青、2 番目は赤であり、その後も同様です。 ここに示した図では、準フェルミ準位はバンドより上に現れ、 電子と正孔は色によって明確に区別されています。 ファイルを追加する順序を変更すると、色もそれに応じて変わります。

snapshots ウィンドウ下部のスライダを使って、電圧掃引を移動してください。 これにより、印加ゲートバイアスの関数として バンド端と準フェルミ準位がどのように変化するかを連続的に追跡できます。

物理的には、この挙動は NMOS コンデンサに対してまさに予想されるものです。 ソース–ドレイン経路は存在せず、構造を貫く DC 電流も流れません。 その結果、電子および正孔の準フェルミ準位は互いに非常に近く、 デバイス全体でほぼ平坦なままです。 現れるわずかな分離は、有限のバイアス刻みによる数値アーティファクトであり、 持続的なキャリア輸送を表すものではありません。

したがって、先に見たバンドベンディングは完全に 静電気学によって駆動されています。すなわち、ゲート電圧が静電ポテンシャルを変化させ、 それによってバンド端が次式に従ってシフトします。

Ec(x) = −q φ(x) − χ and Ev(x) = Ec(x) − Eg

ここで φ は静電ポテンシャル、χ は電子親和力、Eg はバンドギャップです。 準フェルミ準位は単に、これらのバンドが局所的にどのように占有されているかを示すだけであり、 純粋に静電的な MOS コンデンサでは分離しません。

💡 持ち帰るべきこと:

このチュートリアル全体を通して、同じ物理がいくつかの相補的な形で表現されるのを見てきました:

静電ポテンシャル、バンドベンディング、キャリア密度、そしてフェルミ準位です。

これらはすべて、同じ基礎過程 — ゲート制御電場に応答した電荷の再分布 —

を記述しています。

🧪 自分で試してみましょう:

同じ NMOS コンデンサ構造を用いて、材料パラメータおよびバイアスパラメータの変更に対して

静電気学がどのように応答するかを調べてください。すべての場合において、デバイス幾何形状は固定してください。

- SiO2 の誘電率を変更し、同じゲート電圧において シリコン中のポテンシャル降下とバンドベンディングがどのように変化するかを観察してください。

- 基板ドーピング濃度を変更し、空乏幅と バンド端の曲率を比較してください。

- ゲート電圧掃引範囲を広げ、φ、Ec、Ev、 およびキャリア密度がどのように一緒に変化するかを追跡してください。

- シリコン層で Maxwell–Boltzmann 統計と Fermi–Dirac 統計を 切り替え、界面近傍のキャリア密度を比較してください。

期待される結果

- 酸化膜の誘電率を増加させると容量結合が強まり、 印加電圧のより多くの部分がシリコン側にかかるようになります。

- より高い p 型ドーピングでは空乏領域はより狭くなり、 より低いドーピングでは空乏がより広がりバンドベンディングもより緩やかになります。

- バイアス範囲を広げるとバンドベンディングは増加しますが、それだけで コンデンサ幾何において準フェルミ準位が分離することはありません。

- Fermi–Dirac 統計は、高密度時の界面近傍における 非物理的なキャリア過剰占有を抑制します。