NMOS キャパシタチュートリアル(パート A):2D における静電学と空乏化

1. はじめに

MOSFET(Metal–Oxide–Semiconductor Field-Effect Transistor)は、ゲート電圧を用いて 半導体表面でのキャリア密度を静電的に制御することで動作します。MOSFET 物理の最も単純な「原子」は MOS キャパシタです:金属ゲート、絶縁酸化膜、そしてドープされた半導体です。MOS キャパシタを理解すれば、 MOSFET をスイッチさせる静電学を理解したことになります (?? を参照)。

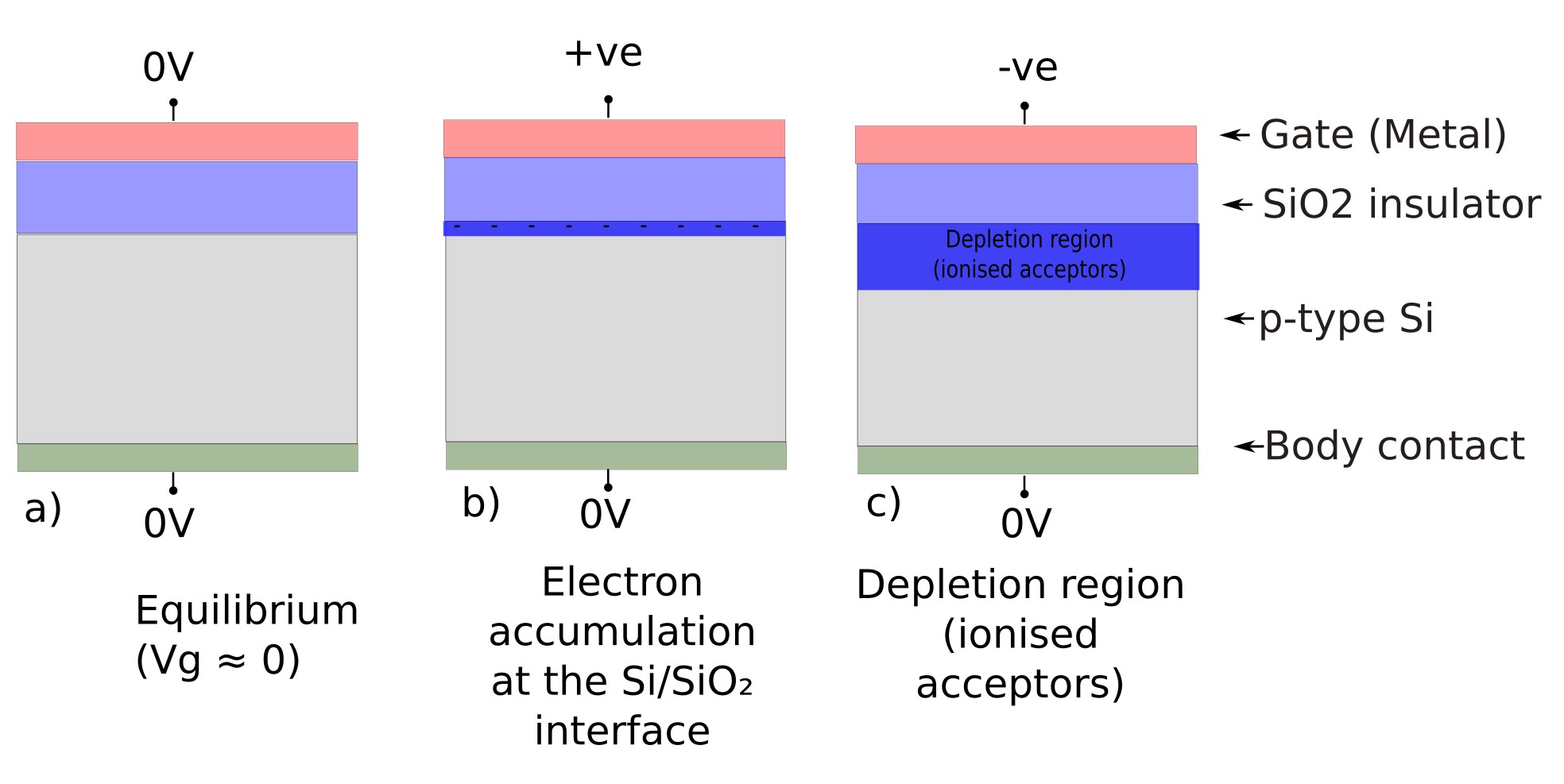

NMOS デバイスが「NMOS」と呼ばれるのは、トランジスタ構造でオンにバイアスされたときに、 n 型反転チャネル—すなわち伝導チャネルのキャリアが電子である状態—を形成するためです。実際には、これは一般に p 型シリコンボディ(アクセプタドープ Si)と十分に正のゲートバイアスによって実現されます。ソースとドレインを導入する前でも、 同じゲート静電学は MOS キャパシタで可視化されます:正のゲートバイアスは電子を Si/SiO2 界面へ引き寄せ(表面蓄積)、一方で負のゲートバイアスは正孔を反発させ、固定されたイオン化アクセプタの領域 (空乏層)を残します。これは ?? に示されています。

PMOS デバイスは補完的な場合であり、p 型チャネル(伝導キャリアとしての正孔)を形成します。一般に 負のゲートバイアス下でn 型ボディを用います。NMOS と PMOS は一緒になって CMOS ロジックで用いられる基本的な補完対を構成します。

このチュートリアルでは、OghmaNano で 2D NMOS キャパシタ構造 を構築して調べます。特に 蓄積領域と空乏領域に焦点を当てます。ここでは物理が静電学に支配されており、結果が解釈しやすいためです。 強反転(真の導電チャネル)はパート B および後続のチュートリアルに委ねます。

2. OghmaNano を起動する

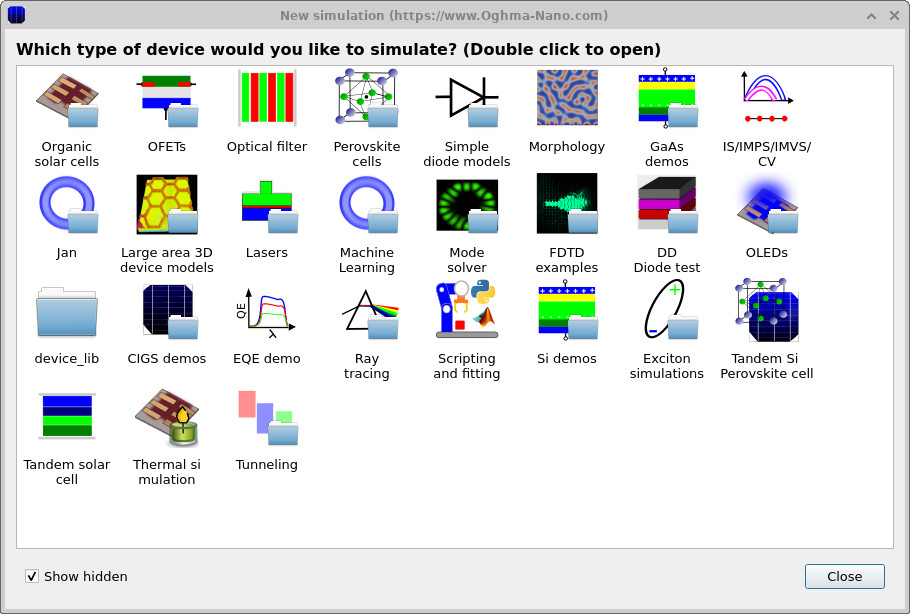

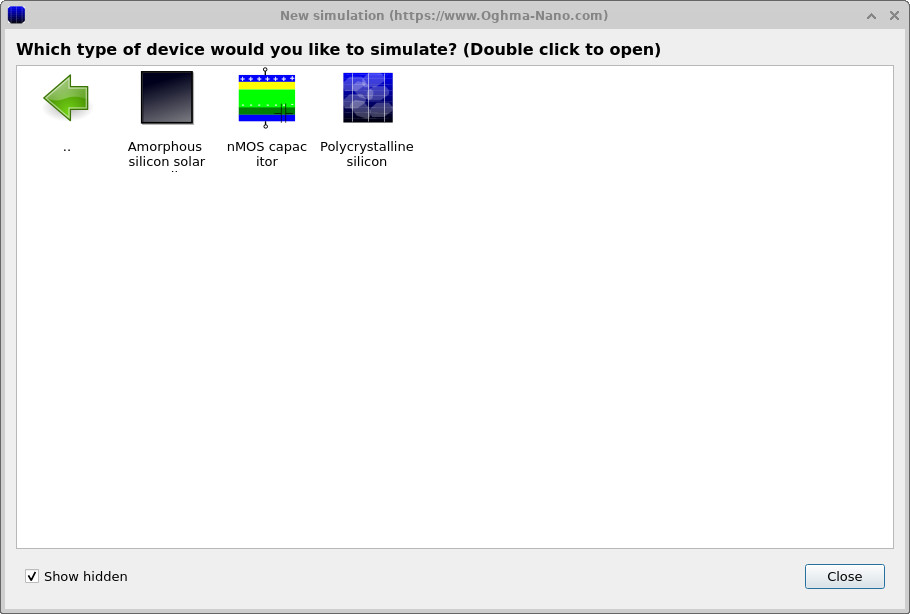

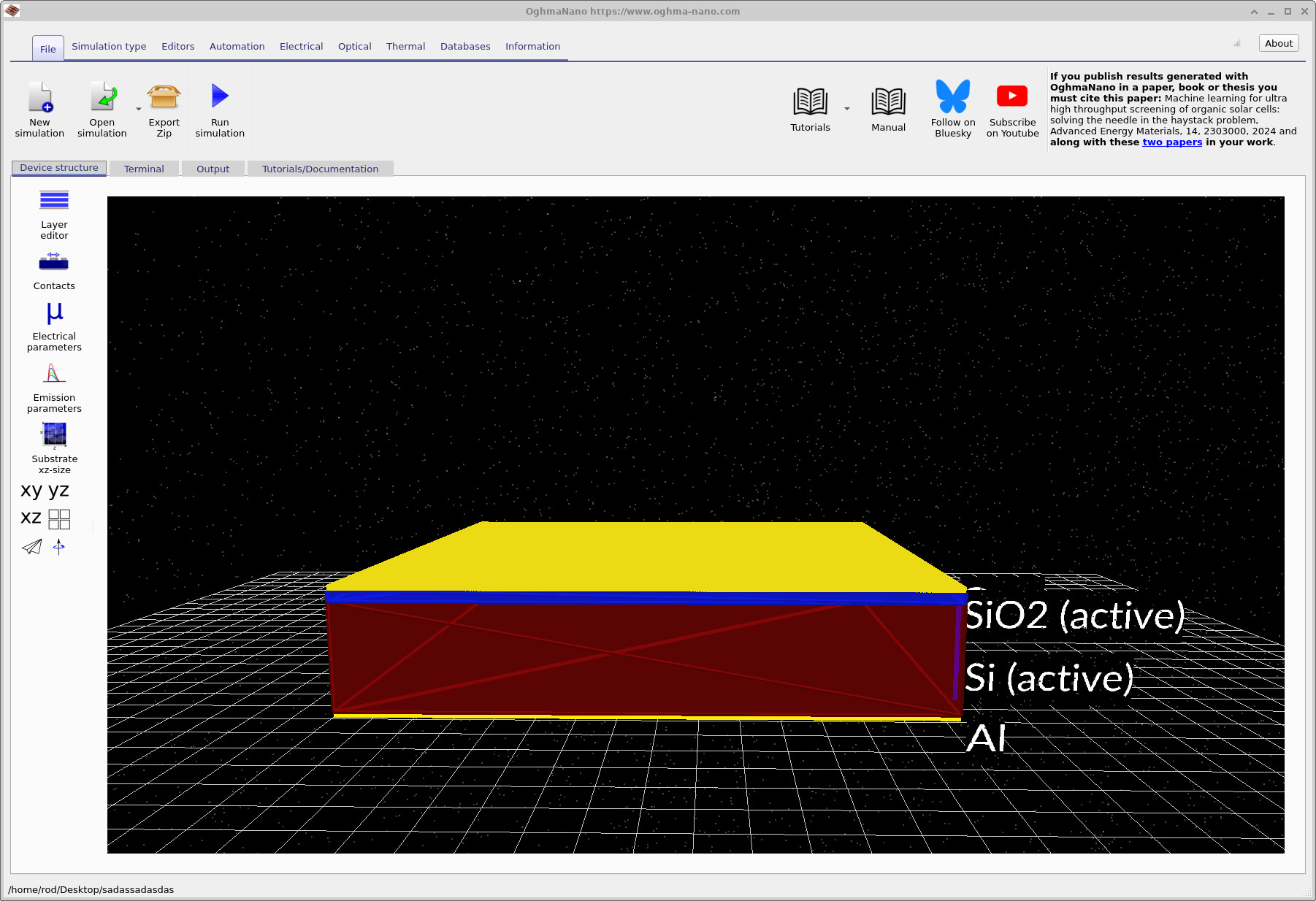

Windows スタートメニューから OghmaNano を起動します。OghmaNano のメインウィンドウが表示されます。これは ?? に示されています。 New simulation をクリックします。これにより、利用可能なデバイスタイプのライブラリが開きます。これは ?? に示されています。 Si demos をダブルクリックしてシリコンの例セットを開き、次に nMOS capacitor の例を選択します。 これは ?? に示されています。 指示が表示されたら、書き込み権限のあるローカルフォルダにシミュレーションを保存してください。保存後、メインシミュレーションウィンドウが 開きます(?? を参照)。

💡 ヒント: 最高の性能を得るため、シミュレーションはローカルドライブ(例:C:\)に保存してください。

ネットワークフォルダやクラウド同期フォルダでは、ソルバーを繰り返し実行する際に速度が低下する場合があります。

3. デバイス構造を確認する(層と材料)

プロジェクトを作成すると、メインシミュレーションウィンドウが開き、意図的に簡略化された NMOS MOS キャパシタ 構造が表示されます:金属ゲート、SiO2 ゲート酸化膜、そして p 型シリコン基板とボディコンタクトです。これは NMOS キャパシタと呼ばれます。なぜなら 半導体ボディが p 型であり、正のゲートバイアスが表面静電学を 電子蓄積へ向かわせるためです。この構造は典型的な NMOS 静電学構成を表しており、 Si/SiO2 界面におけるバンドベンディング、蓄積、および空乏化を研究するために広く用いられています。

実際のデバイスでは、MOS キャパシタはより複雑なレイアウトに組み込まれていたり、 追加のコンタクトと組み合わされていたりすることがよくあります。ここでは、それらの要素を意図的に省略して、 焦点を完全に NMOS キャパシタ自体の垂直静電学に絞っています。横方向輸送と 幾何学的複雑さを取り除くことで、半導体における電荷再分布と静電ポテンシャル 変化の物理的起源を、直接かつ曖昧さなく調べることができます。

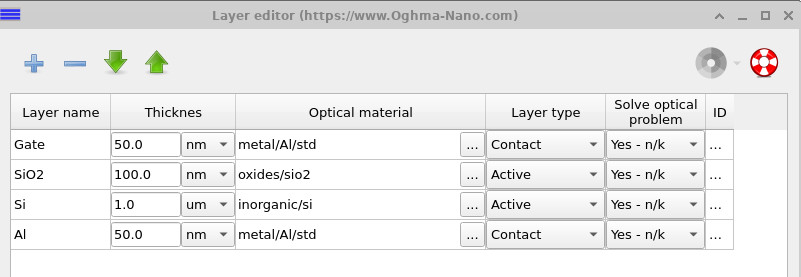

層構造は Layer editor で確認できます。分かりやすくするために、この チュートリアルにおける酸化膜厚は、現代のシリコン技術よりもやや大きく選ばれています。これにより、出力プロットで 生じる電位降下、蓄積層、および空乏領域が明確に見えるようになります。 現代の NMOS キャパシタでは、酸化膜厚は通常 10 nm 以下程度です。チュートリアル完了後には、層 厚を調整し、構造がより現実的な デバイス寸法に近づくにつれて静電応答がどのように変化するかを調べてみてください。

4. Electrical リボンと 2D メッシュを確認する

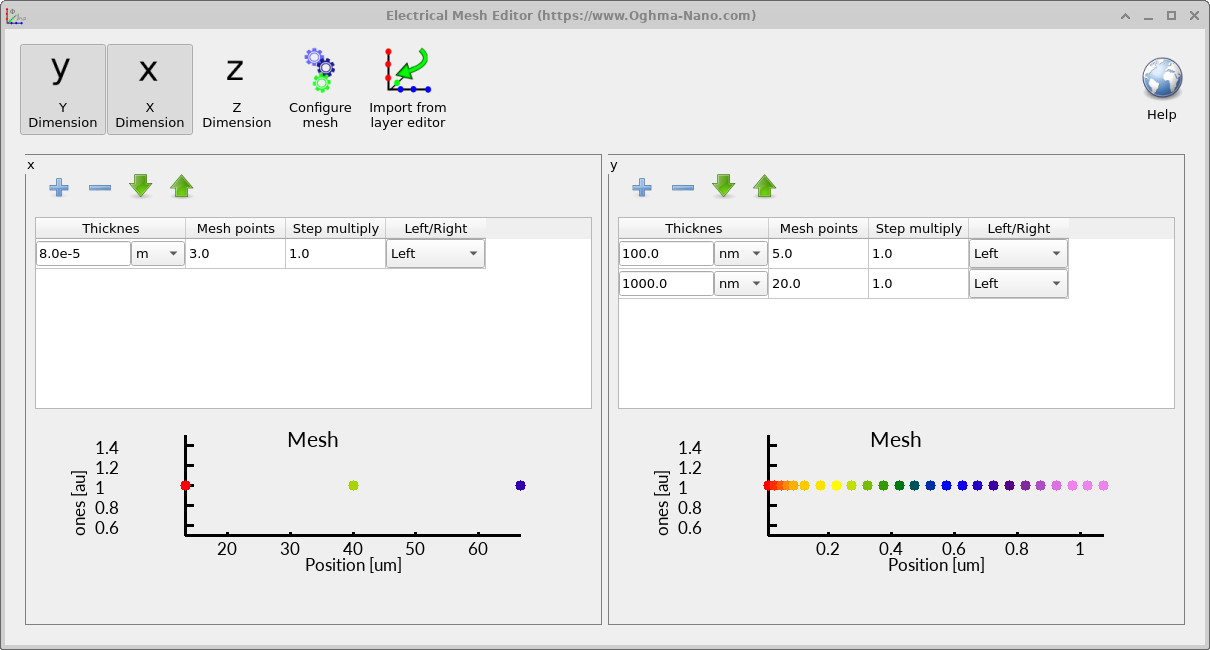

NMOS キャパシタのワークフローの大部分は Electrical リボンにあります。ここから、どの電気モデルを有効にするかを選択し、 パラメータを編集し、ドーピングを確認し、メッシュを設定できます。 Electrical mesh をクリックするとメッシュエディタが開きます(?? を参照)。

このチュートリアルでは 2D メッシュ を使用します:デバイスは 2 次元で離散化され、界面近傍のバンドベンディングと空乏化を捉えつつ、 計算時間を短く保ちます。ここで示されている例では、一方向(横方向)の点数は少なく、 酸化膜厚およびシリコン厚方向(垂直方向)には、静電勾配が存在するため、より密なサンプリングが配置されています。メッシュ点数を増やすことはできますが、 計算コストは未知数の数にほぼ比例して増加します(また、非線形問題ではバイアスポイントあたりの反復回数にも依存します)。

5. Electrical Parameter Editor(酸化膜とシリコン)

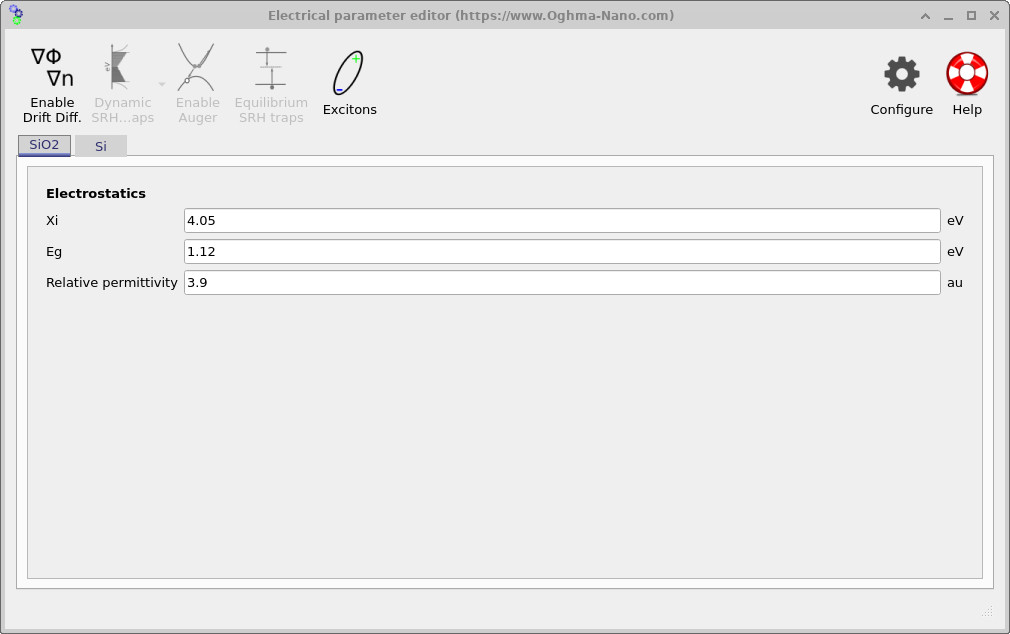

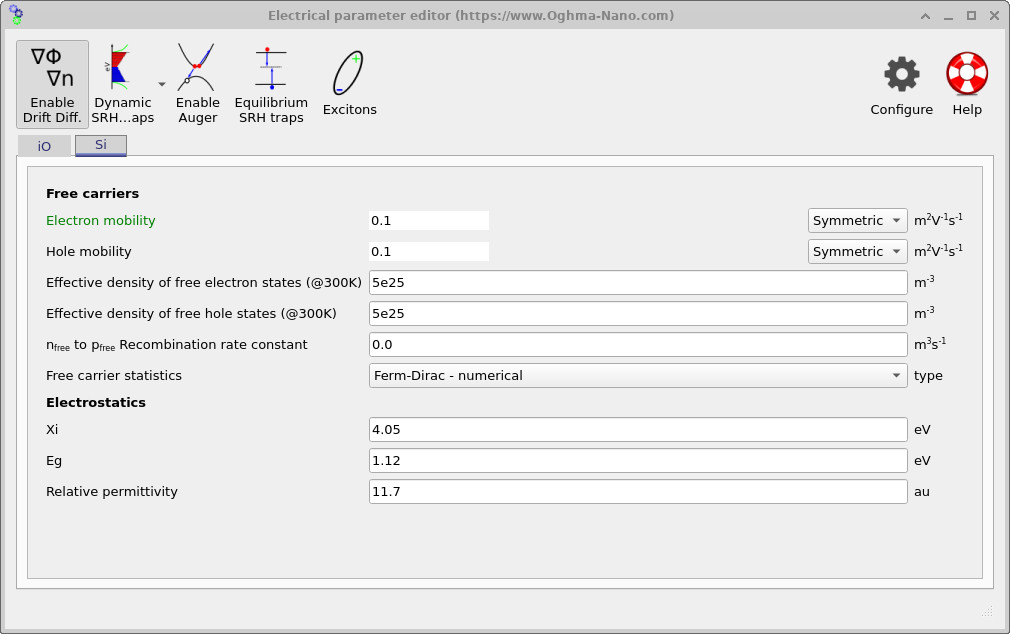

Electrical parameters をクリックすると Electrical Parameter Editor が開きます。このエディタは材料ごとに整理されています: SiO2 タブには酸化膜パラメータがあり、Si タブにはシリコンパラメータがあります。 シリコン層については、物理的に妥当なパラメータセットを使用します:相対誘電率は約 11.7、電子親和力とバンドギャップは標準的なシリコン値、電子および正孔の移動度は有限値、 状態密度の有効値も現実的です。重要なのは、 Maxwell–Boltzmann 統計ではなく Fermi–Dirac 統計 を選択する点です。これは、ゲートバイアス下では Si/SiO2 界面近傍のキャリア密度が 縮退効果が重要になるほど高くなり得るためです。

対照的に、酸化膜層では、このチュートリアルで中心的な役割を果たすパラメータは 相対誘電率のみです。SiO2 は理想絶縁体として扱われます:電場 と電圧降下は支えますが、移動電荷は支えません。その結果、NMOS キャパシタの静電挙動は、印加ゲート電圧が酸化膜とシリコンの間でどのように分割されるかによって支配され、 これは酸化膜厚と誘電率によって 完全に決定されます。

このモデリング選択は、エディタ上部のボタンにも反映されています。SiO2 層では、 drift–diffusion は無効であり、Poisson 方程式のみが解かれます。これに対して、 シリコン 層では drift–diffusion が有効であり、ゲートバイアスに応答した 電子と正孔の再分布を正しく捉えることができます。この分離は、NMOS キャパシタにおける 2 つの材料の物理的役割を反映しています: 酸化膜は電場を媒介し、シリコンは移動キャリアを担います。

SiO2 に記載されている 電子親和力 や バンドギャップ のようなパラメータが シリコンのものと似ているように見えるかもしれません。このチュートリアルの文脈では、それは意図的であり、問題ありません。 酸化膜ではキャリア輸送方程式が解かれないため、これらのバンドパラメータは解に影響しません: モデル内では電子や正孔が酸化膜に入る機構が存在しないからです。したがって SiO2 は その電子バンド構造を通じてではなく、誘電応答を通じてのみ 寄与します。

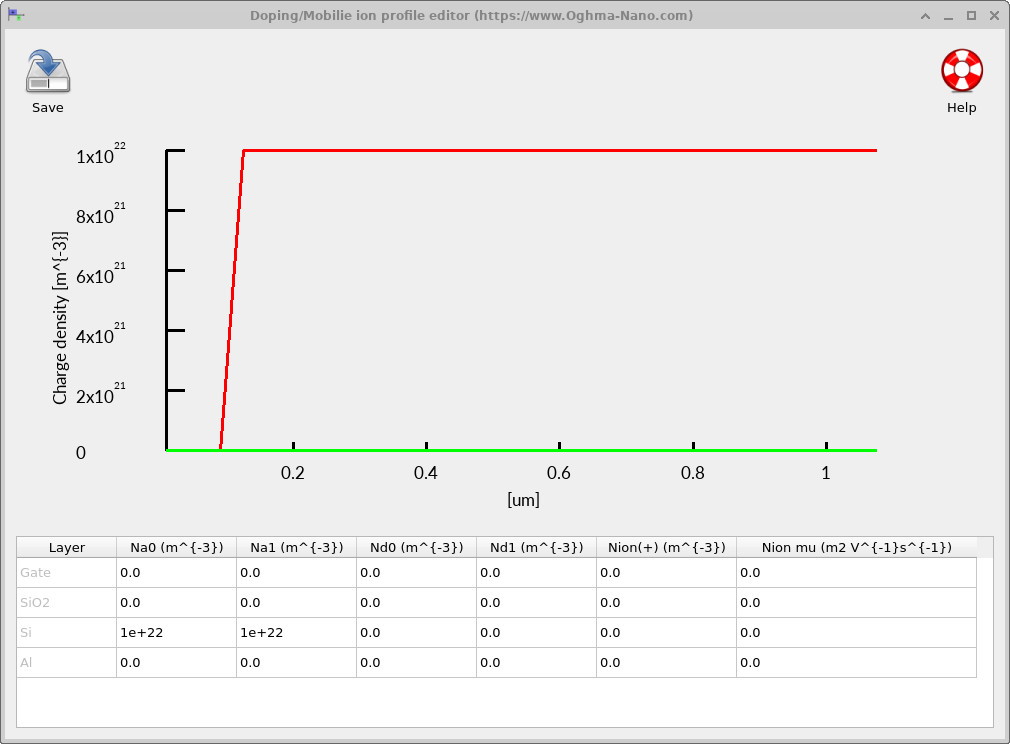

6. Doping editor(基板ドーピングプロファイル)

最後に、Electrical リボンから Doping エディタを開いて、ドーパント分布を確認してください (?? を参照)。 NMOS キャパシタでは、シリコン基板は通常 p 型(アクセプタドープ)です。 ゼロまたは負のゲートバイアスでは、正孔が Si/SiO2 界面近傍の多数キャリアです。 ゲートバイアスが正になると、ゲート電場が正孔を表面から押しのけ、 イオン化アクセプタ(固定負電荷)を残して 空乏領域を形成します。

ドーパント濃度はキャパシタの静電応答を強く制御します。 より高い p 型ドーピングでは、与えられた表面電位に対して より薄い空乏領域 となり、 より低いドーピングでは より広い空乏領域 と、より大きなバンドベンディングの空間的広がりが生じます。 パート B では、このエディタを用いて基板ドーピングを意図的に変更し、その結果として生じる 空乏幅、静電ポテンシャル、およびバンド構造の変化を観察します。

7. シミュレーションを実行する(Terminal 出力)

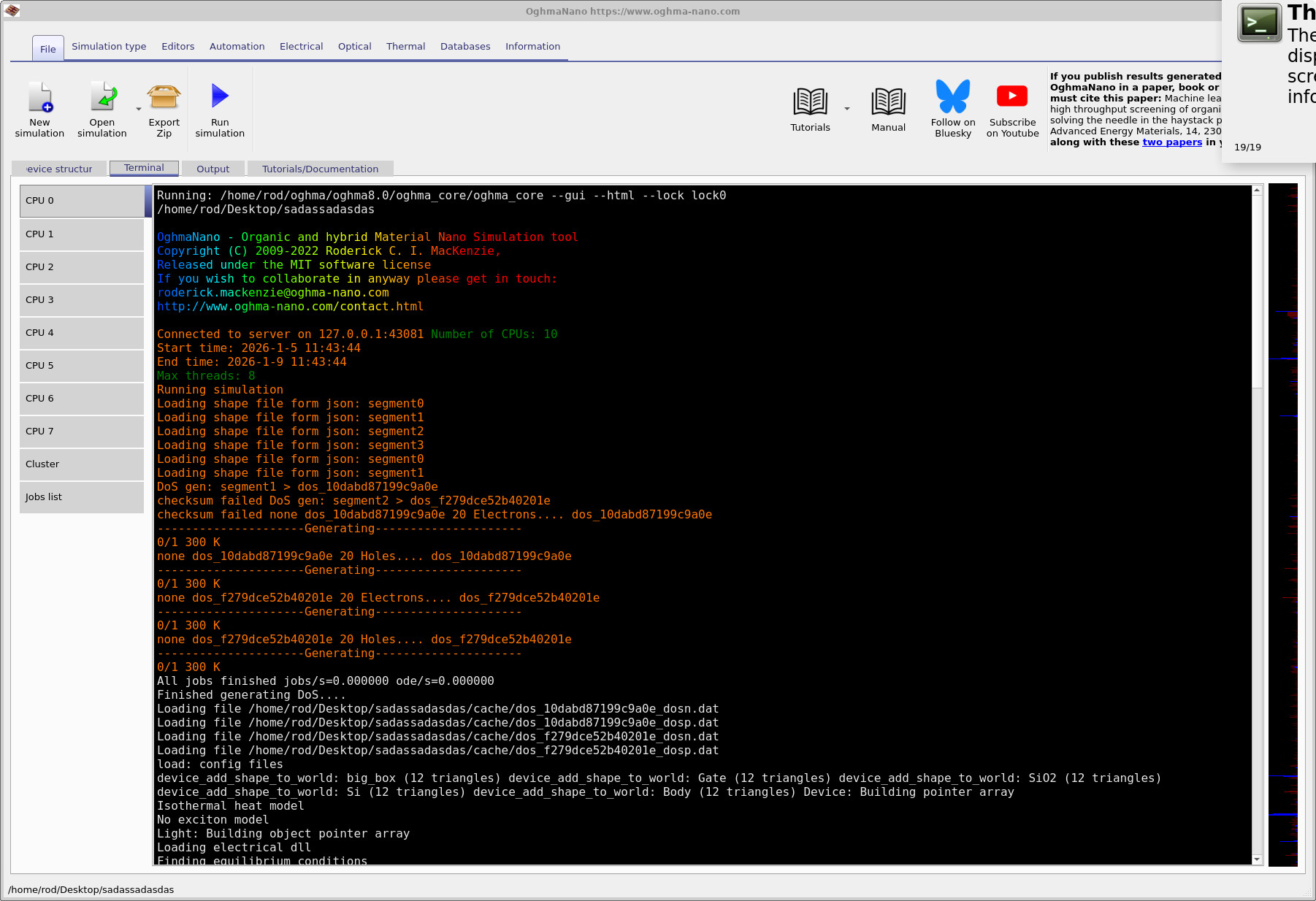

メインウィンドウで Run simulation(青い矢印)をクリックします。OghmaNano は Terminal タブへ切り替わり、ソルバーの実行を開始します。典型的な実行の最初の段階は ?? に示されています。ここでは、コアソルバーを起動するために用いられたコマンドライン、 続いてプロジェクトの読み込みとモデル初期化が見えます。繰り返し表示される Generating... 行は、OghmaNano が Fermi–Dirac 統計のルックアップテーブルを構築していることを示しています(選択した層の電子と正孔について)。Fermi–Dirac 積分を 高精度に評価するのは計算コストが高いため、コードはこれらの量を一度テーブル化し、その後の非線形反復で再利用します。Loading file が表示されるときは、 キャッシュされたテーブル(またはその他のキャッシュされた中間データ)を再読み込みしており、毎回の実行で再生成するのを避けています。

もう一つの重要な段階は バイアスランピング です。メインスイープを開始する前に、ソルバーは既知で収束しやすい開始点 (通常は平衡付近)から、要求された最初のバイアスポイント(ここでは -2 V)までゲートを徐々にランプします。これは継続法です: Newton 型ソルバーは、初期推定が解に十分近いときにのみ、信頼性よく収束します。大きなバイアスへ直接飛ぶと、 初期推定が「離れすぎた」状態になり、発散や遅く不安定な収束を引き起こすことがあります。ゲート電圧を小刻みに 変化させることで、各解が次の解の良い初期推定になります。

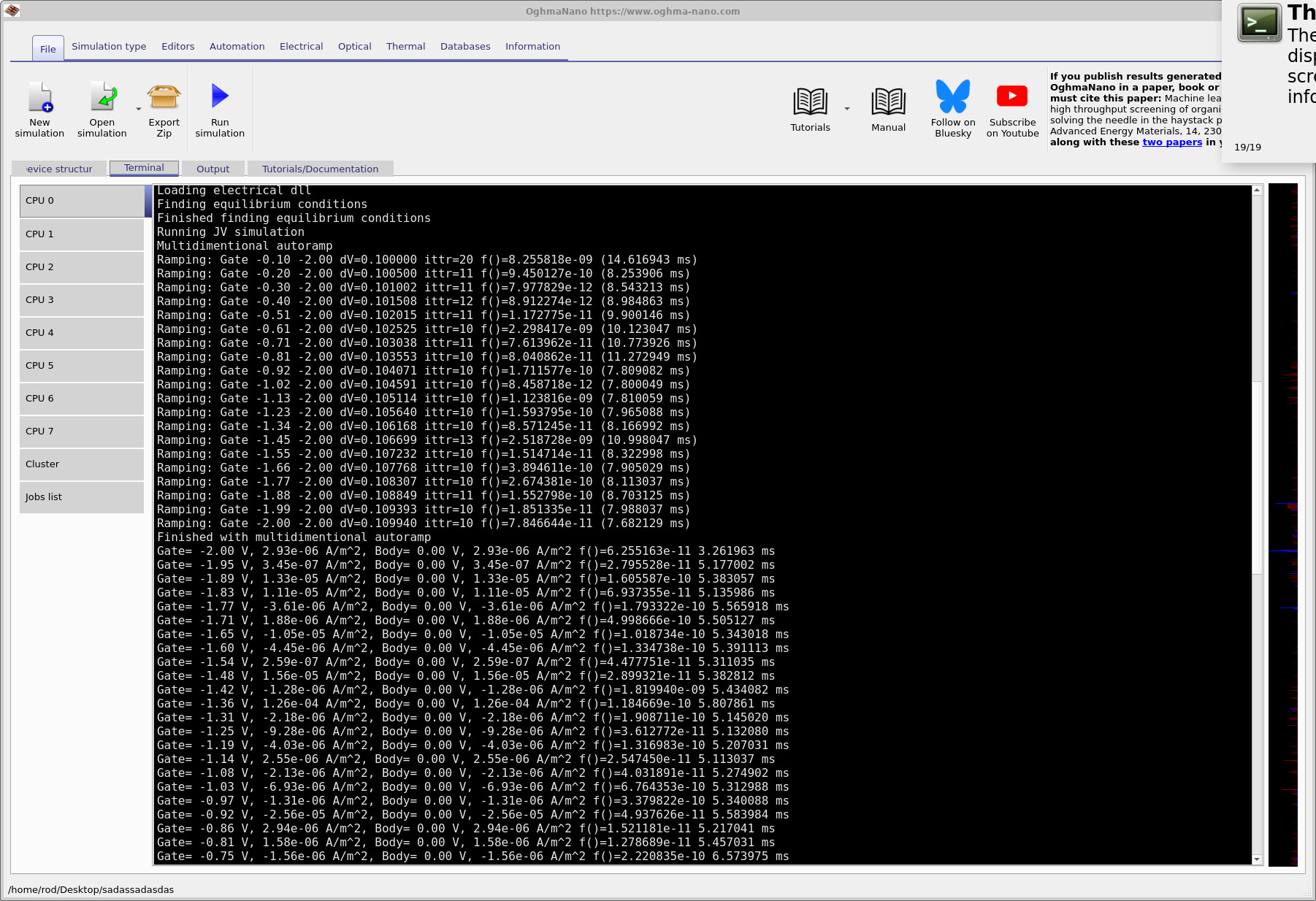

ゲートが開始電圧に到達すると、ソルバーはゲートスイープ(「J–V」/バイアス曲線)を進めます。デバイスボディは 0 V に保持されます(Terminal に表示されている通りです)。キャパシタは本来(ほとんど)ゼロの定常 DC 電流しか持たないにもかかわらず、 表示される電流密度の符号と大きさが変動することに気づくかもしれません。ここではその挙動は正常です:ソルバーは、非線形解法の 数値ノイズフロア近傍にある非常に小さな残留電流を報告しています。言い換えると、その「スパイク状」の挙動は物理的な DC 電流ではなく、 本当に ~0 である量を高い相対精度で計算しようとしていることによる症状です。

f(...)= として報告される量は、非線形残差/誤差尺度(収束指標)です。この値が非常に小さいとき、

静電解(ポテンシャル、電荷、バンドベンディング)は収束したとみなされます。右側に表示される時間(ミリ秒)は、

バイアスステップ/反復ブロックごとの実行時間であり、プロファイリングやメッシュ密度増加のコストを判断するのに有用です。

f(...) 値はソルバー残差(収束指標)です。

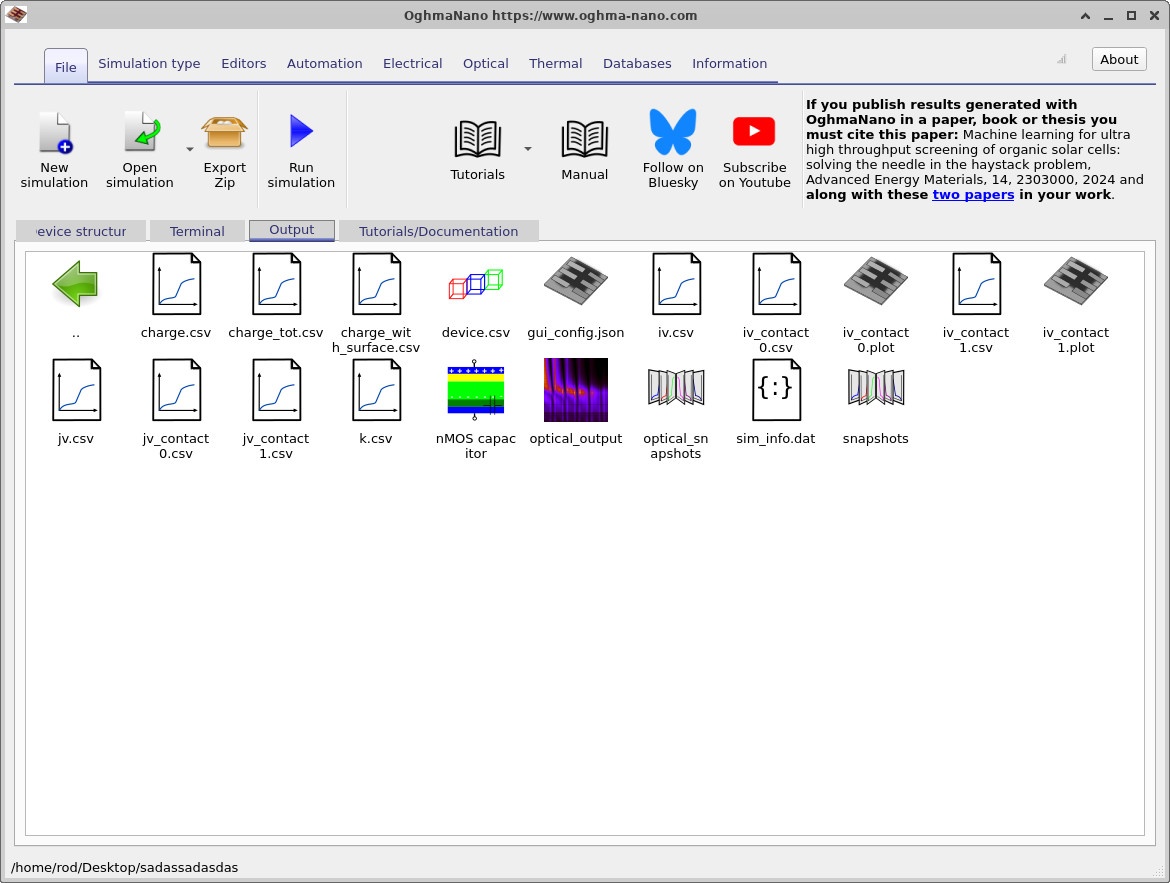

8. 出力ファイルとコンタクト電流

実行が完了したら、Output タブに切り替えてシミュレーションによって生成されたファイルを表示します

(?? を参照)。

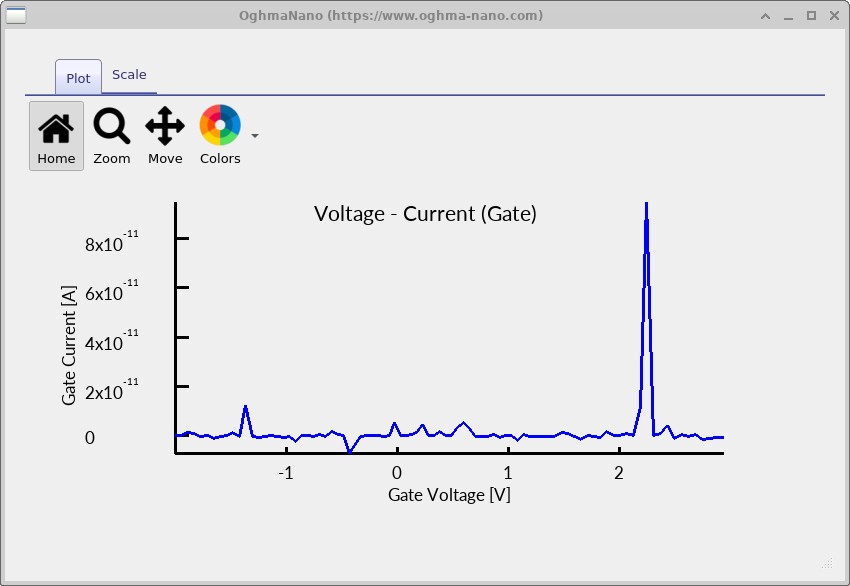

iv_contact_0.csv や iv_contact_1.csv のような項目をダブルクリックすると、コンタクト電流プロットを開くことができます。

理想的な MOS キャパシタでは、構造が純粋に静電的であるため、定常 DC 電流は本質的にゼロです。 したがって、コンタクト電流プロットは主に背景情報および完全性のために含まれており、 意図しない電流経路が存在しないことを確認するための簡単な 健全性チェックとして機能します。曲線はバイアススイープ全体を通じてゼロに近いままであるべきであり、 小さな変動は正常で、真の電流が極めて小さいことを反映しているにすぎません。

次のセクションでは、これらの補助的な出力を離れ、 シミュレーションの物理的に意味のある結果である静電ポテンシャル、バンド端、 Fermi 準位、および NMOS キャパシタ内部のキャリア分布に焦点を当てます。

💡 ここまでで学んだこと: このチュートリアルでは、NMOS キャパシタシミュレーションを設定して確認しました (デバイス構造、メッシュ、材料パラメータ、およびドーピング)。 パート B では、これを基にゲートバイアスを印加し、 シミュレーション出力—バンドベンディング、静電ポテンシャル、 キャリア密度、および表面空乏化—を解釈します。