Tutorial de Capacitor NMOS (Parte A): Eletrostática e Depleção em 2D

1. Introdução

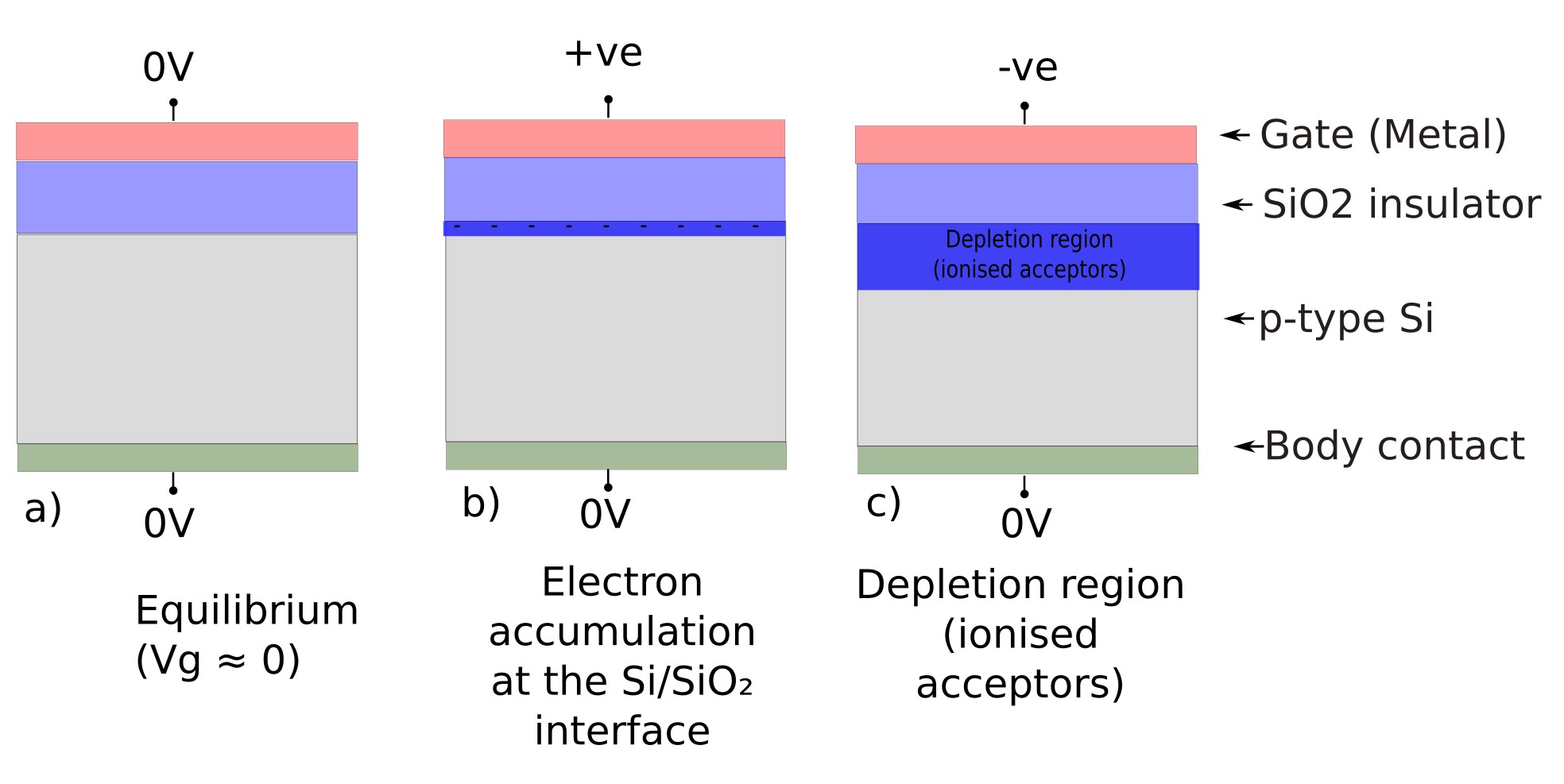

Um MOSFET (Metal–Oxide–Semiconductor Field-Effect Transistor) funciona usando uma tensão de porta para controlar eletrostaticamente a densidade de portadores em uma superfície semicondutora. O “átomo” mais simples da física de MOSFET é o capacitor MOS: uma porta metálica, um óxido isolante e um semicondutor dopado. Se você entende o capacitor MOS, entende a eletrostática que faz um MOSFET comutar (veja ??).

Um dispositivo NMOS é chamado “NMOS” porque, quando polarizado em condução em uma geometria de transistor, ele forma um canal de inversão do tipo n — os portadores condutores do canal são elétrons. Na prática, isso é comumente realizado com um corpo de silício tipo p (Si dopado com aceitadores) e uma polarização de porta suficientemente positiva. Mesmo antes de introduzir fonte e dreno, a mesma eletrostática de porta é visível no capacitor MOS: uma polarização positiva de porta atrai elétrons para a interface Si/SiO2 (acumulação superficial), enquanto uma polarização negativa de porta repele lacunas e deixa para trás uma região de aceitadores ionizados fixos (depleção), como ilustrado em ??.

Um dispositivo PMOS é o caso complementar: ele forma um canal do tipo p (lacunas como portadores condutores), comumente usando um corpo do tipo n sob polarização negativa de porta. NMOS/PMOS juntos formam o par complementar básico usado em lógica CMOS.

Neste tutorial, construímos e exploramos uma estrutura de capacitor NMOS 2D no OghmaNano. Focamos deliberadamente nos regimes de acumulação e depleção, onde a física é dominada pela eletrostática e os resultados são fáceis de interpretar. A inversão forte (um verdadeiro canal condutor) é deixada para a Parte B e tutoriais posteriores.

2. Inicie o OghmaNano

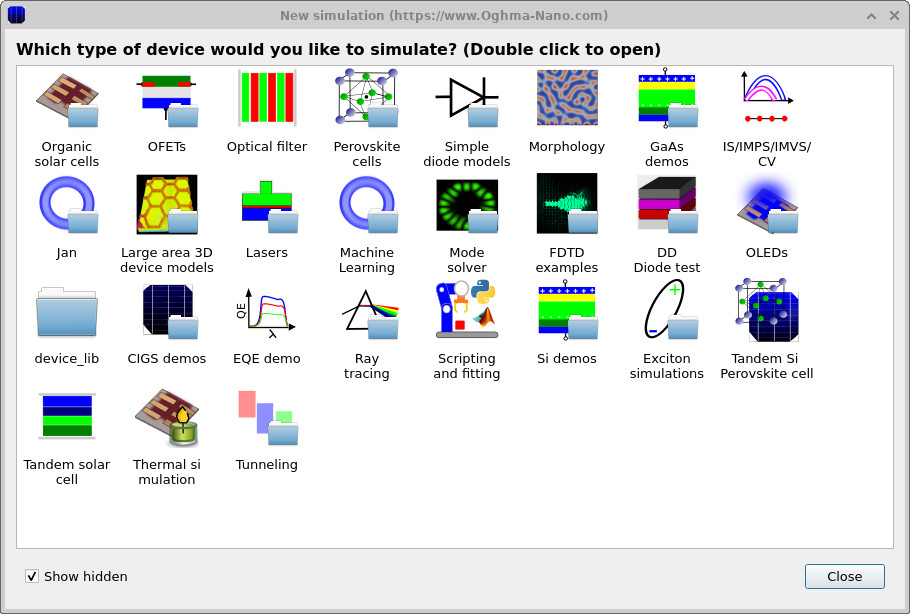

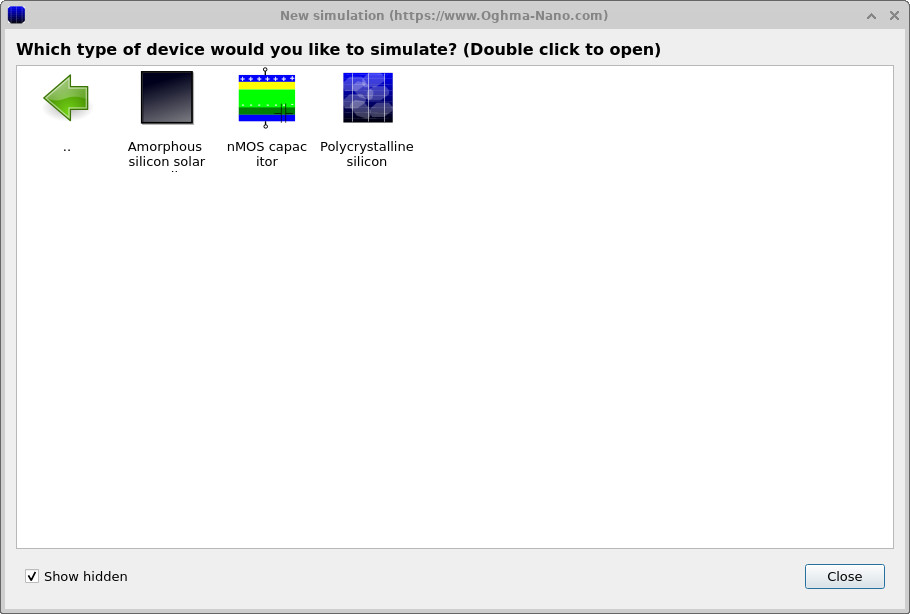

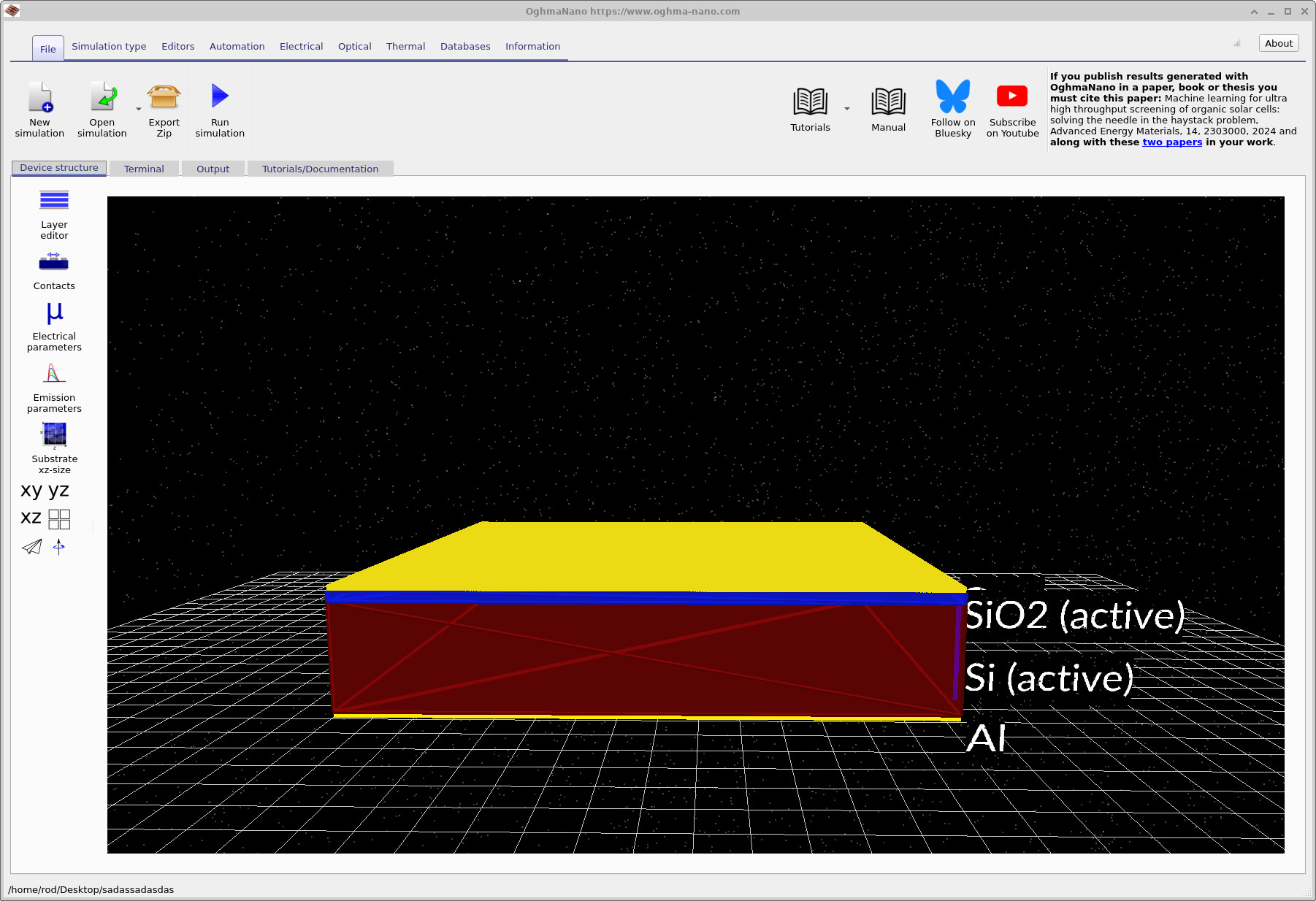

Inicie o OghmaNano a partir do menu Iniciar do Windows. A janela principal do OghmaNano aparecerá como mostrado em ??. Clique em New simulation. Isso abre a biblioteca de tipos de dispositivos disponíveis, mostrada em ??. Clique duas vezes em Si demos para abrir o conjunto de exemplos de silício, depois selecione o exemplo nMOS capacitor como mostrado em ??. Quando solicitado, salve a simulação em uma pasta local com permissão de escrita. Após salvar, a janela principal da simulação é aberta (veja ??).

💡 Dica: Salve simulações em uma unidade local (por exemplo, C:\) para melhor desempenho.

Pastas de rede ou sincronizadas na nuvem podem tornar execuções repetidas do solver mais lentas.

3. Inspecione a estrutura do dispositivo (camadas e materiais)

Após criar o projeto, a janela principal da simulação é aberta mostrando uma estrutura de capacitor MOS NMOS deliberadamente simplificada: uma porta metálica, um óxido de porta de SiO2 e um substrato de silício tipo p com um contato de corpo. Ela é chamada de capacitor NMOS porque o corpo semicondutor é do tipo p, e uma polarização positiva de porta leva a eletrostática superficial em direção à acumulação de elétrons. Essa estrutura representa a configuração eletrostática canônica de NMOS e é amplamente usada para estudar curvatura de bandas, acumulação e depleção na interface Si/SiO2.

Em dispositivos práticos, o capacitor MOS é frequentemente embutido em layouts mais complexos ou combinado com contatos adicionais. Aqui, esses elementos são intencionalmente omitidos para que o foco permaneça inteiramente na eletrostática vertical do próprio capacitor NMOS. Ao remover transporte lateral e complexidade geométrica, a origem física da redistribuição de carga e da variação do potencial eletrostático no semicondutor pode ser examinada diretamente e sem ambiguidade.

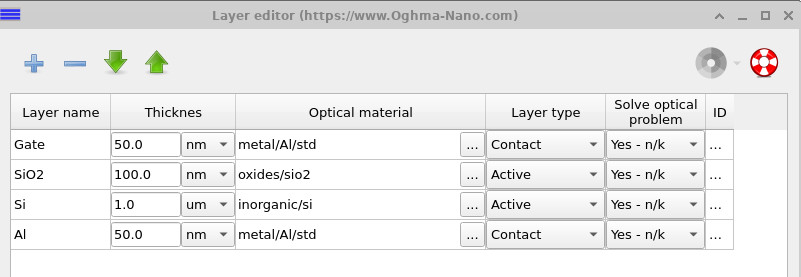

A estrutura em camadas pode ser inspecionada no Layer editor. Para maior clareza, a espessura do óxido neste tutorial foi escolhida para ser ligeiramente maior do que na tecnologia moderna de silício, de modo que a queda de potencial resultante, a camada de acumulação e a região de depleção sejam claramente visíveis nos gráficos de saída. Em capacitores NMOS contemporâneos, as espessuras de óxido são tipicamente da ordem de 10 nm ou menos. Após concluir o tutorial, recomenda-se que você ajuste as espessuras das camadas e explore como a resposta eletrostática muda à medida que a estrutura se aproxima de dimensões realistas de dispositivo.

4. Inspecione a faixa elétrica e a malha 2D

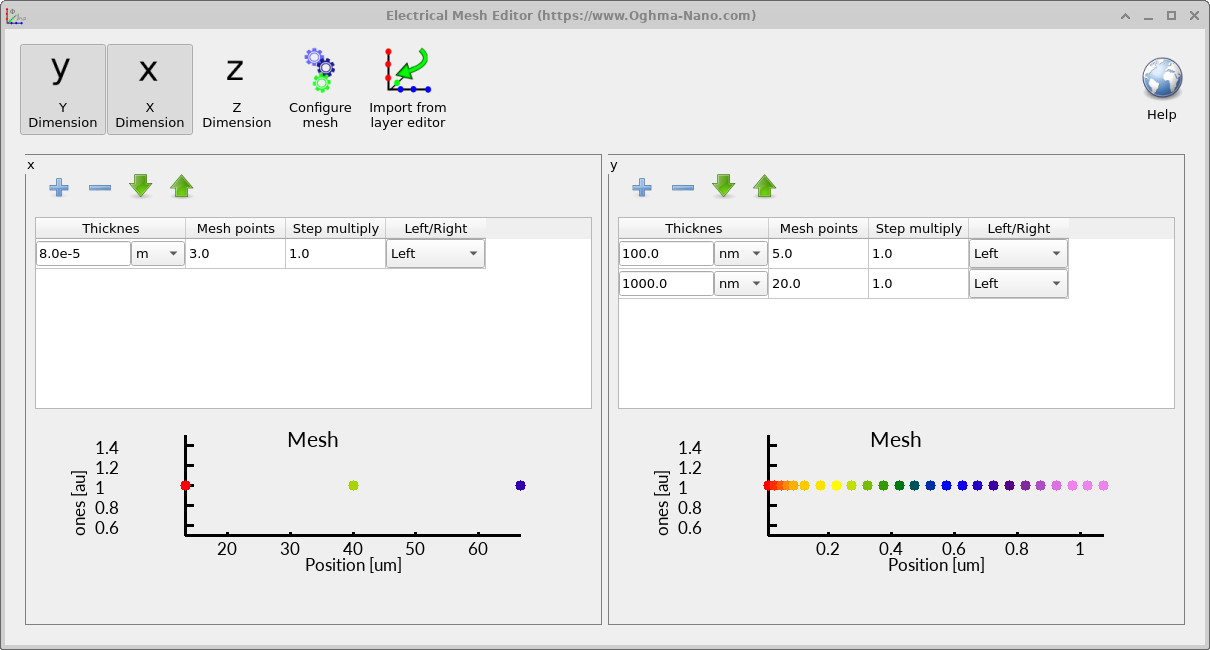

A maior parte do fluxo de trabalho do capacitor NMOS está na faixa Electrical. A partir dela, você pode escolher qual modelo elétrico está ativo, editar parâmetros, inspecionar dopagem e configurar a malha. Clicar em Electrical mesh abre o editor de malha (veja ??).

Este tutorial usa uma malha 2D: o dispositivo é resolvido em duas dimensões para capturar a curvatura de bandas e a depleção próximas à interface enquanto mantém tempos de execução curtos. No exemplo mostrado, há apenas alguns pontos ao longo de uma direção (lateral) e uma amostragem mais densa ao longo da espessura do óxido e do silício (vertical), onde estão os gradientes eletrostáticos. Você pode aumentar o número de pontos da malha, mas o custo computacional cresce aproximadamente com o número de incógnitas (e, para problemas não lineares, com o número de iterações por ponto de polarização).

5. Editor de Parâmetros Elétricos (óxido vs silício)

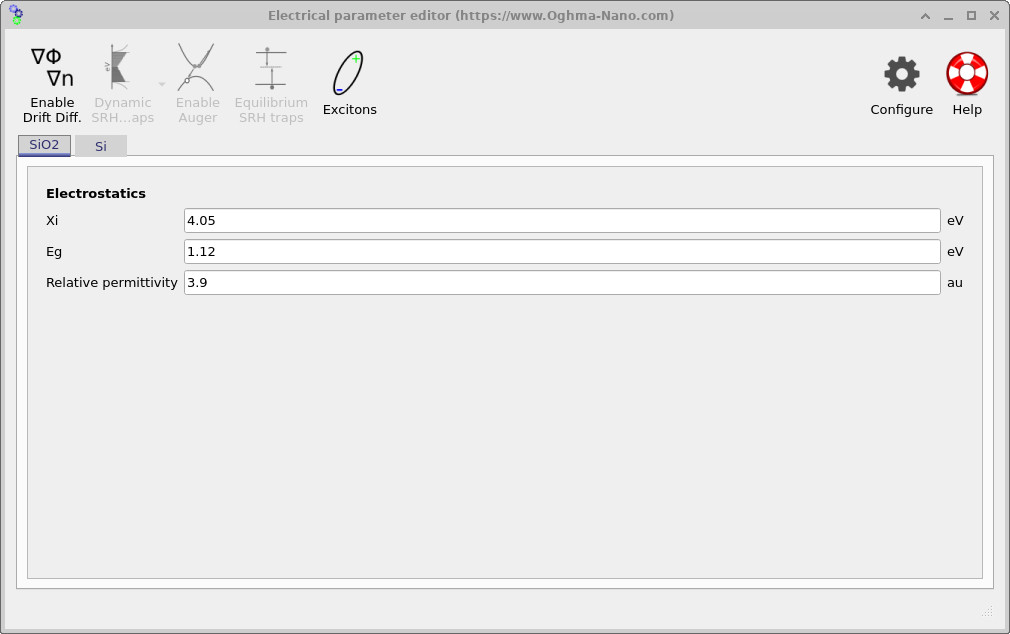

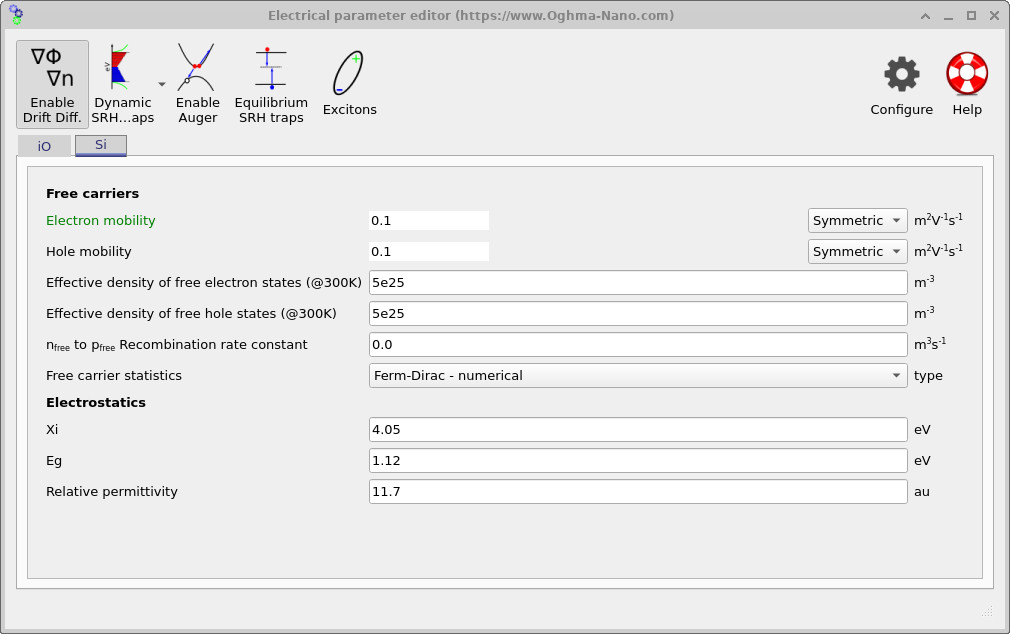

Clicar em Electrical parameters abre o Editor de Parâmetros Elétricos. Esse editor é organizado por material: a aba SiO2 contém parâmetros do óxido, enquanto a aba Si contém parâmetros do silício. Para a camada de silício, usamos um conjunto de parâmetros fisicamente sensato: uma permissividade relativa de aproximadamente 11.7, valores padrão de silício para afinidade eletrônica e band gap, mobilidades finitas de elétrons e lacunas, e densidades efetivas de estados realistas. É importante destacar que selecionamos estatística de Fermi–Dirac em vez de estatística de Maxwell–Boltzmann, já que, sob polarização de porta, a densidade de portadores próxima à interface Si/SiO2 pode se tornar alta o suficiente para que efeitos de degenerescência sejam importantes.

Para a camada de óxido, por outro lado, o único parâmetro que desempenha papel central neste tutorial é a permissividade relativa. O SiO2 é tratado como um isolante ideal: ele sustenta um campo elétrico e uma queda de tensão, mas não suporta carga móvel. Como resultado, o comportamento eletrostático do capacitor NMOS é governado por como a tensão aplicada à porta se divide entre o óxido e o silício, o que é determinado inteiramente pela espessura e pela permissividade do óxido.

Essa escolha de modelagem é refletida nos botões na parte superior do editor. Na camada de SiO2, drift–diffusion está desativado, de modo que apenas a equação de Poisson é resolvida ali. Em contraste, na camada de silício, drift–diffusion está ativado para que a redistribuição de elétrons e lacunas em resposta à polarização de porta possa ser capturada corretamente. Essa separação espelha os papéis físicos dos dois materiais em um capacitor NMOS: o óxido media o campo elétrico, enquanto o silício hospeda os portadores móveis.

Você pode notar que parâmetros como a afinidade eletrônica e o band gap listados para SiO2 parecem semelhantes aos do silício. No contexto deste tutorial, isso é intencional e inofensivo. Como as equações de transporte de portadores não são resolvidas no óxido, esses parâmetros de banda não influenciam a solução: não há mecanismo para que elétrons ou lacunas entrem no óxido no modelo. O SiO2, portanto, participa apenas por meio de sua resposta dielétrica, não por sua estrutura de bandas eletrônica.

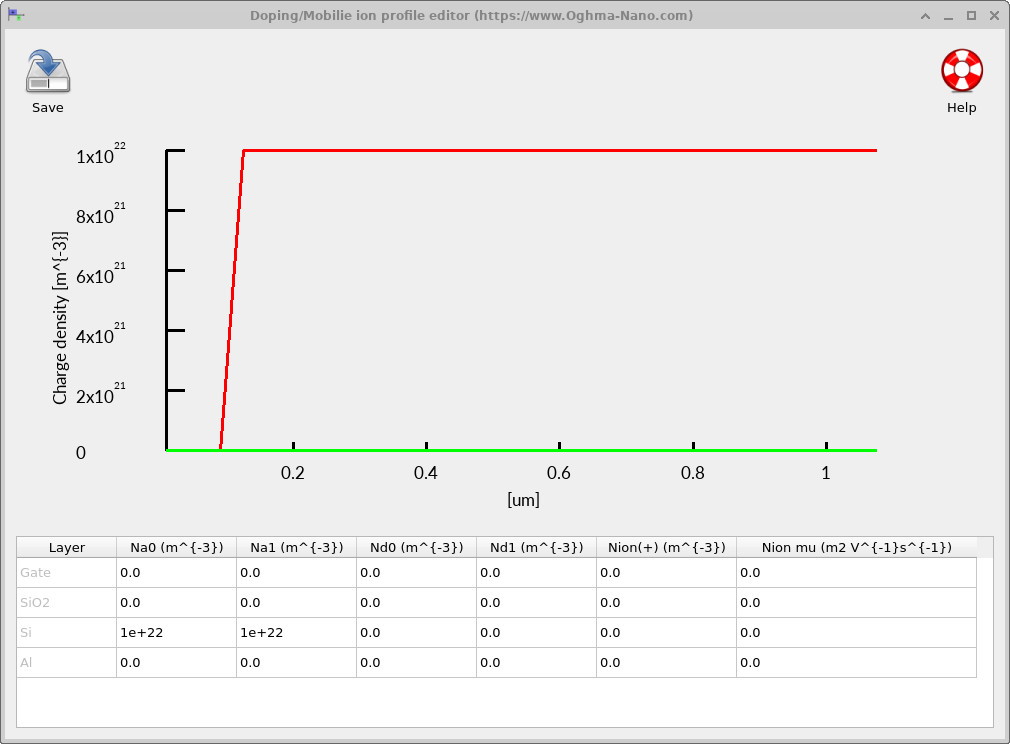

6. Editor de dopagem (perfil de dopagem do substrato)

Por fim, abra o editor de Doping na faixa Electrical para inspecionar a distribuição de dopantes (veja ??). Para um capacitor NMOS, o substrato de silício é tipicamente tipo p (dopado com aceitadores). Em polarização de porta nula ou negativa, lacunas são os portadores majoritários próximos à interface Si/SiO2. À medida que a polarização de porta se torna positiva, o campo elétrico da porta repele lacunas da superfície, deixando para trás aceitadores ionizados (carga negativa fixa) e formando uma região de depleção.

A concentração de dopantes controla fortemente a resposta eletrostática do capacitor. Uma dopagem tipo p mais intensa resulta em uma região de depleção mais fina para um dado potencial de superfície, enquanto uma dopagem mais leve produz uma região de depleção mais larga e uma maior extensão espacial da curvatura de bandas. Na Parte B, usaremos esse editor para modificar deliberadamente a dopagem do substrato e observar as mudanças resultantes na largura de depleção, no potencial eletrostático e na estrutura de bandas.

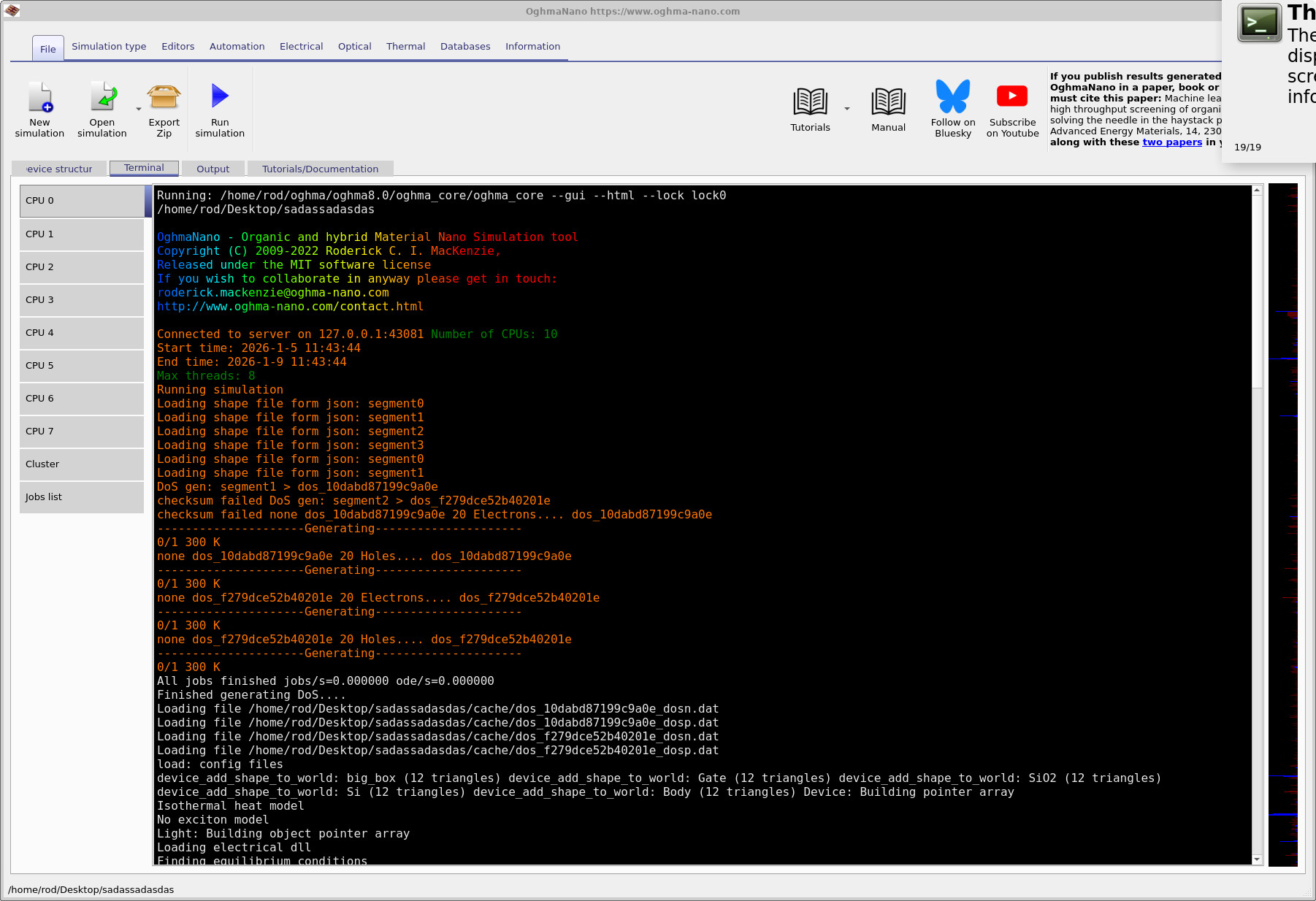

7. Execute a simulação (saída do Terminal)

Clique em Run simulation (a seta azul) na janela principal. OghmaNano irá alternar para a aba Terminal e começará a executar o solver. O primeiro estágio de uma execução típica é mostrado em ??; ali você pode ver a linha de comando usada para iniciar o solver principal, seguida pelo carregamento do projeto e pela inicialização do modelo. As linhas repetidas Generating... indicam que o OghmaNano está construindo tabelas de consulta para estatística de Fermi–Dirac (para elétrons e lacunas nas camadas que você selecionou). Avaliar integrais de Fermi–Dirac com precisão é caro computacionalmente, então o código tabula essas quantidades uma vez e depois as reutiliza durante as iterações não lineares. Quando você vê Loading file, ele está recarregando as tabelas em cache (ou outros dados intermediários em cache) para evitar regenerá-las a cada execução.

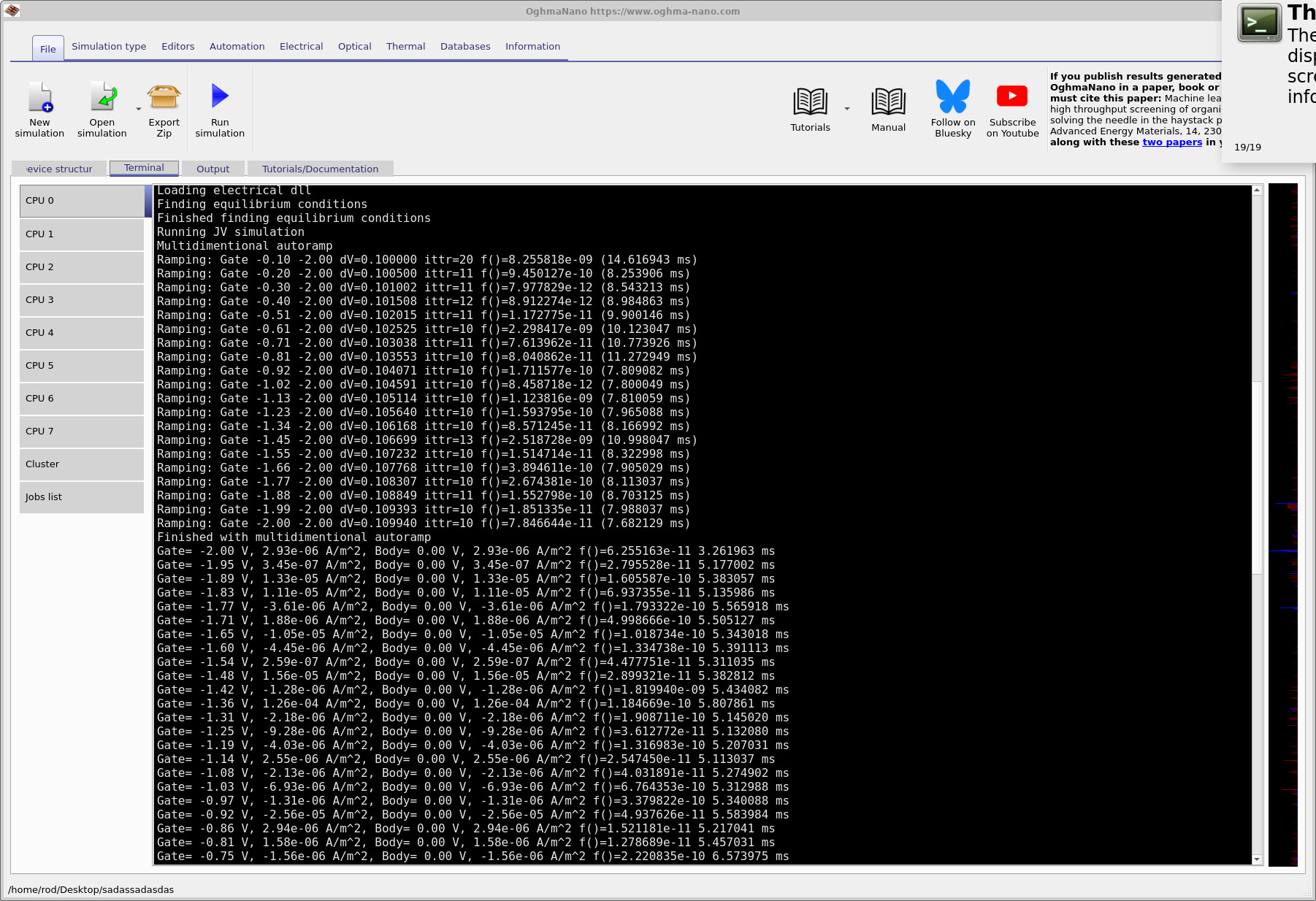

Um segundo estágio importante é a rampa de polarização. Antes que a varredura principal comece, o solver gradualmente leva a porta de um ponto inicial conhecido e fácil (tipicamente próximo do equilíbrio) até o primeiro ponto de polarização solicitado (aqui, até -2 V). Essa é uma estratégia de continuação: solvers do tipo Newton convergem de forma confiável apenas quando a estimativa inicial está razoavelmente próxima da solução. Saltar diretamente para uma grande polarização pode colocar a estimativa inicial “longe demais”, causando divergência ou convergência lenta e instável. Ao variar a tensão de porta em pequenos incrementos, cada solução fornece uma boa estimativa inicial para a seguinte.

Assim que a porta atinge a tensão inicial, o solver prossegue com a varredura de porta (a curva “J–V”/polarização). O corpo do dispositivo é mantido em 0 V (como informado no terminal). Você pode notar que a densidade de corrente impressa flutua em sinal e magnitude, embora um capacitor deva ter corrente DC em regime permanente (essencialmente) nula. Esse comportamento é normal aqui: o solver está reportando correntes residuais muito pequenas, próximas ao piso de ruído numérico da solução não linear. Em outras palavras, a “oscilação” não é uma corrente DC física; é um sintoma de tentar calcular uma grandeza que é realmente ~0 com alta precisão relativa.

A grandeza reportada como f(...)= é a medida de residual/erro não linear (uma métrica de convergência). Quando esse valor é muito pequeno,

a solução eletrostática (potencial, carga, curvatura de bandas) é considerada convergida. O tempo mostrado à direita (em milissegundos) é o

tempo de execução por etapa de polarização / bloco de iteração, e é útil para profiling e para avaliar o custo de aumentar a densidade da malha.

f(...) é o residual do solver (métrica de convergência).

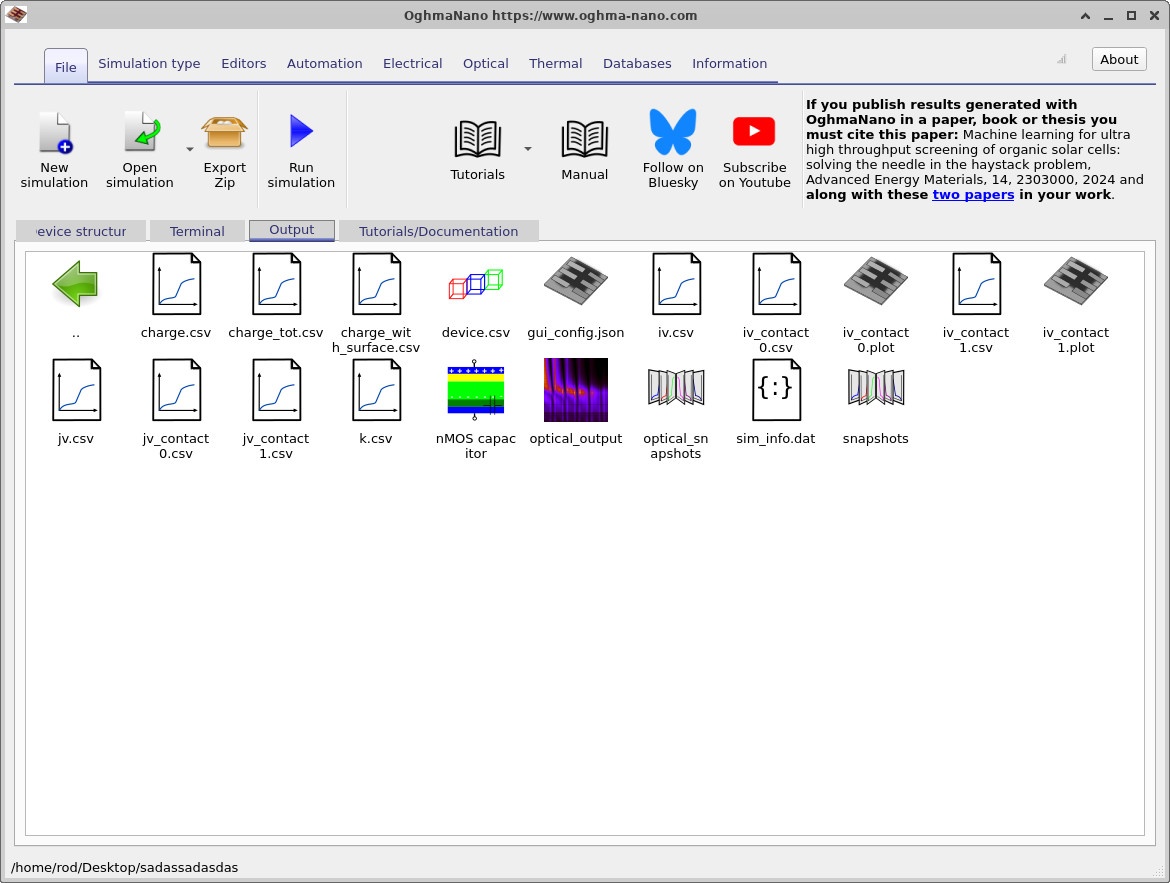

8. Arquivos de saída e corrente de contato

Quando a execução terminar, mude para a aba Output para ver os arquivos produzidos pela simulação

(veja ??).

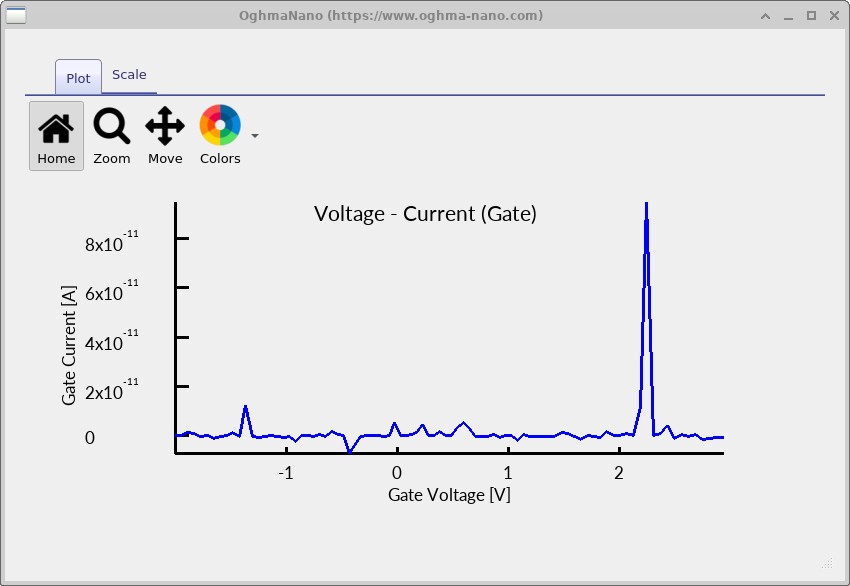

Você pode clicar duas vezes em entradas como iv_contact_0.csv e iv_contact_1.csv para abrir os gráficos de corrente de contato.

Para um capacitor MOS ideal, a corrente DC em regime permanente é essencialmente zero, uma vez que a estrutura é puramente eletrostática. Os gráficos de corrente de contato são, portanto, incluídos principalmente por contexto e completude, e como uma simples verificação de consistência de que não existem caminhos de corrente não intencionais. As curvas devem permanecer próximas de zero ao longo da varredura de polarização; pequenas flutuações são normais e simplesmente refletem o fato de que a corrente real é extremamente pequena.

Na próxima seção, iremos além dessas saídas auxiliares e focaremos nos resultados fisicamente significativos da simulação: o potencial eletrostático, bordas de banda, níveis de Fermi e distribuições de portadores dentro do capacitor NMOS.

💡 O que você aprendeu até agora: Neste tutorial, você configurou e inspecionou uma simulação de capacitor NMOS (estrutura do dispositivo, malha, parâmetros de material e dopagem). Na Parte B, construiremos sobre isso aplicando polarização de porta e interpretando a saída da simulação — curvatura de bandas, potencial eletrostático, densidades de portadores e depleção superficial.