Tutorial de condensador NMOS (Parte A): Electrostática y agotamiento en 2D

1. Introducción

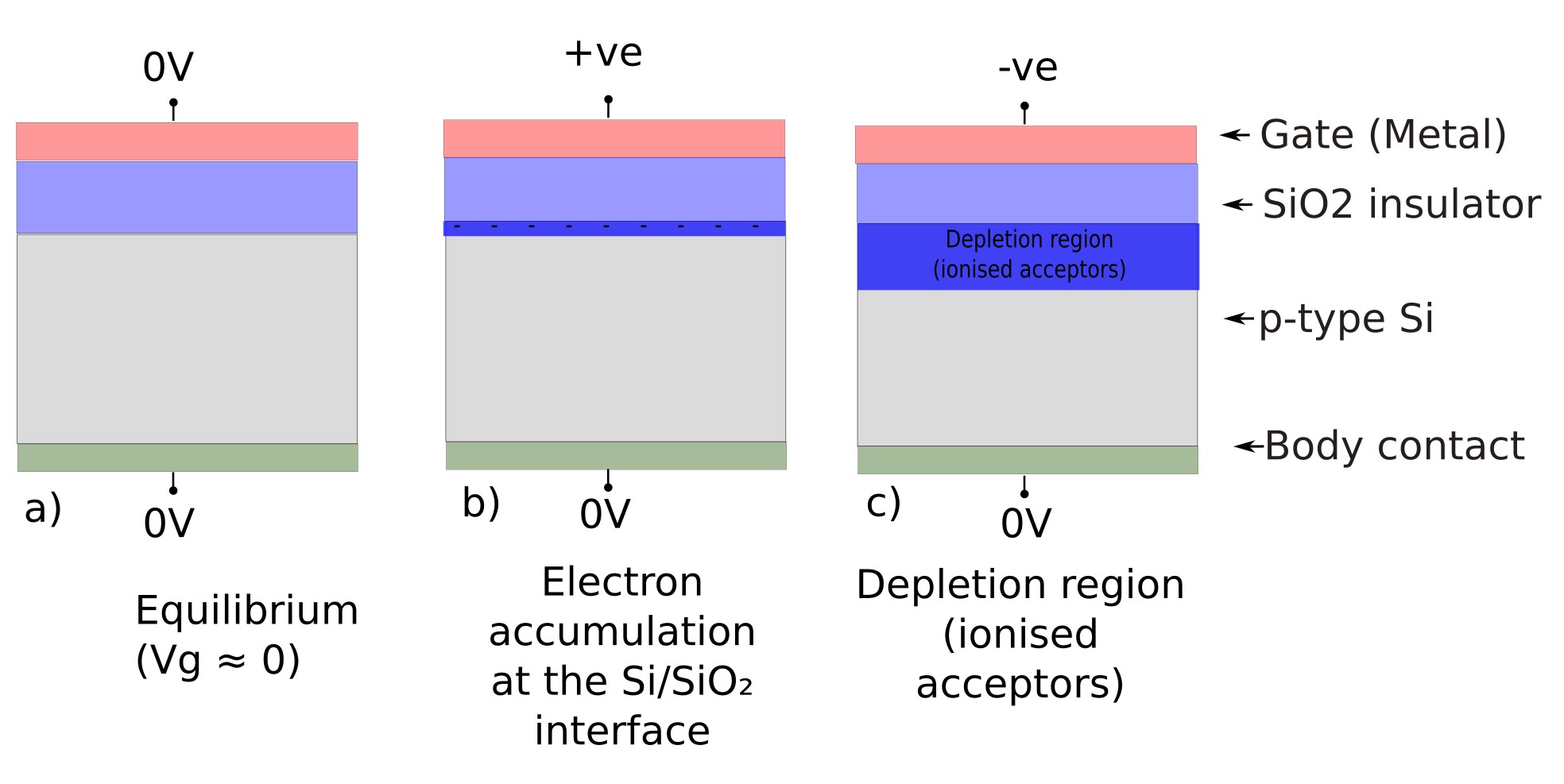

Un MOSFET (transistor de efecto de campo metal–óxido–semiconductor) funciona usando un voltaje de compuerta para controlar electrostáticamente la densidad de portadores en una superficie semiconductora. El “átomo” más simple de la física de un MOSFET es el condensador MOS: una compuerta metálica, un óxido aislante y un semiconductor dopado. Si comprende el condensador MOS, comprende la electrostática que hace que un MOSFET conmute (véase ??).

Un dispositivo NMOS se llama “NMOS” porque, cuando se polariza en conducción en una geometría de transistor, forma un canal de inversión tipo n—los portadores conductores del canal son electrones. En la práctica, esto se realiza habitualmente con un cuerpo de silicio tipo p (Si dopado con aceptores) y una polarización de compuerta suficientemente positiva. Incluso antes de introducir fuente y drenador, la misma electrostática de compuerta es visible en el condensador MOS: una polarización positiva de compuerta atrae electrones hacia la interfaz Si/SiO2 (acumulación superficial), mientras que una polarización negativa de compuerta repele huecos y deja atrás una región de aceptores ionizados fijos (agotamiento), como se ilustra en ??.

Un dispositivo PMOS es el caso complementario: forma un canal tipo p (huecos como portadores conductores), utilizando habitualmente un cuerpo tipo n bajo polarización negativa de compuerta. NMOS/PMOS forman juntos el par complementario básico usado en la lógica CMOS.

En este tutorial construimos y exploramos una estructura de condensador NMOS 2D en OghmaNano. Nos centramos deliberadamente en los regímenes de acumulación y agotamiento, donde la física está dominada por la electrostática y los resultados son fáciles de interpretar. La inversión fuerte (un canal verdaderamente conductor) se deja para la Parte B y tutoriales posteriores.

2. Iniciar OghmaNano

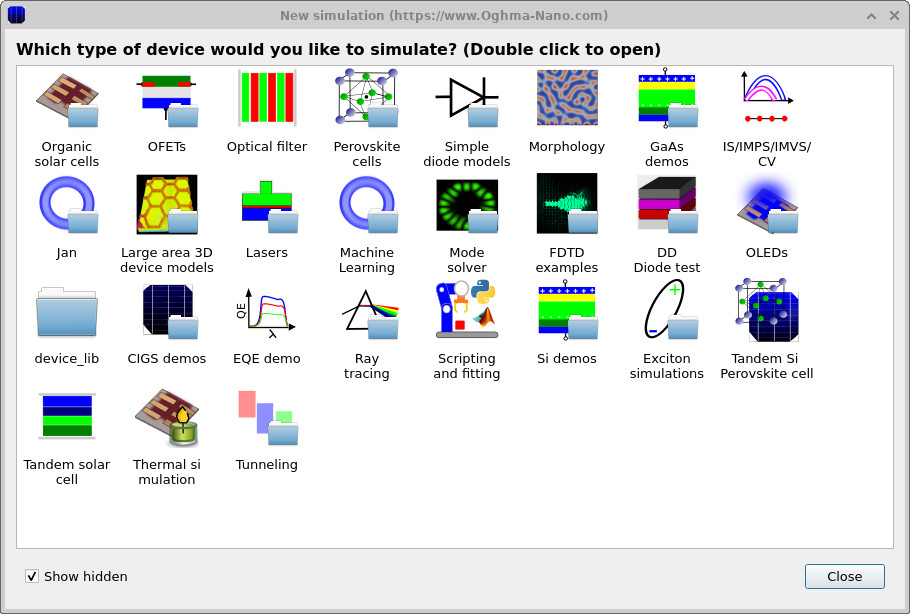

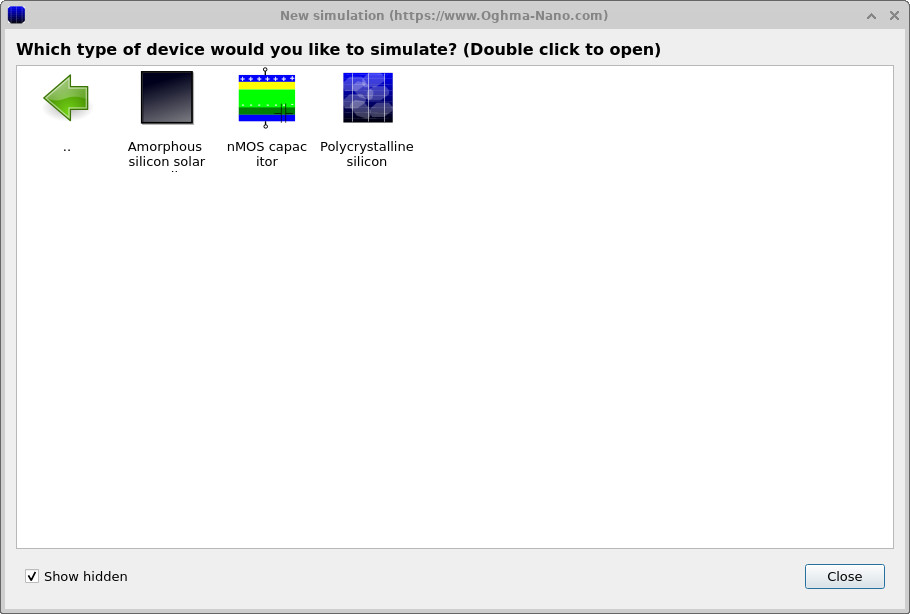

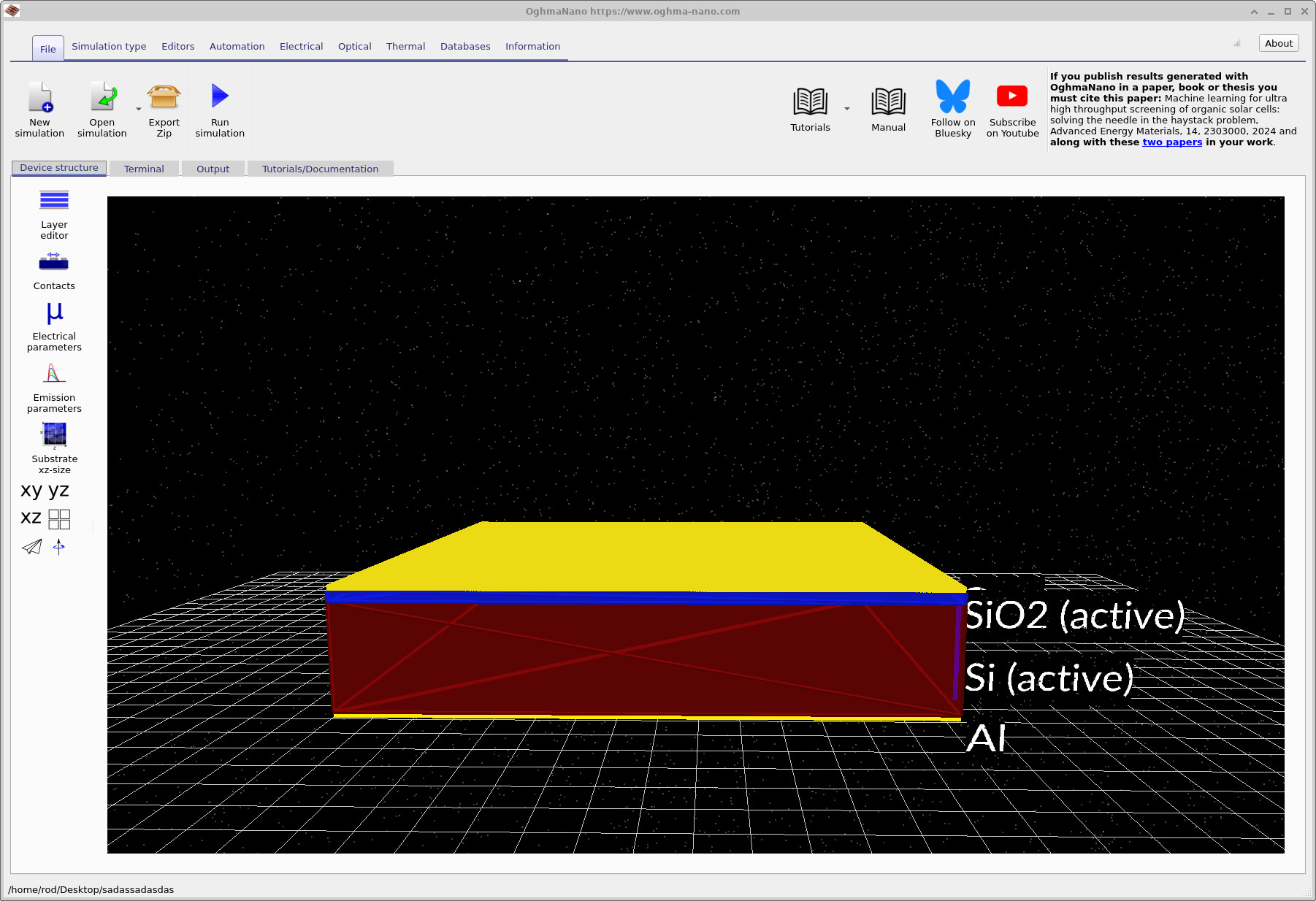

Inicie OghmaNano desde el menú Inicio de Windows. La ventana principal de OghmaNano aparecerá como se muestra en ??. Haga clic en Nueva simulación. Esto abre la biblioteca de tipos de dispositivo disponibles, mostrada en ??. Haga doble clic en Demostraciones de Si para abrir el conjunto de ejemplos de silicio, y después seleccione el ejemplo condensador nMOS como se muestra en ??. Cuando se le solicite, guarde la simulación en una carpeta local con permisos de escritura. Después de guardar, la ventana principal de simulación se abre (véase ??).

💡 Consejo: Guarde las simulaciones en una unidad local (p. ej. C:\) para obtener el mejor rendimiento.

Las carpetas de red o respaldadas en la nube pueden ralentizar ejecuciones repetidas del solucionador.

3. Inspeccionar la estructura del dispositivo (capas y materiales)

Después de crear el proyecto, la ventana principal de simulación se abre mostrando una estructura de condensador MOS NMOS deliberadamente simplificada: una compuerta metálica, un óxido de compuerta de SiO2 y un sustrato de silicio tipo p con un contacto de cuerpo. Se denomina condensador NMOS porque el cuerpo semiconductor es tipo p, y una polarización positiva de compuerta lleva la electrostática superficial hacia la acumulación de electrones. Esta estructura representa la configuración electrostática canónica de un NMOS y se usa ampliamente para estudiar la curvatura de bandas, la acumulación y el agotamiento en la interfaz Si/SiO2.

En dispositivos prácticos, el condensador MOS suele estar embebido dentro de disposiciones más complejas o combinado con contactos adicionales. Aquí, esos elementos se omiten intencionadamente para que el foco permanezca completamente en la electrostática vertical del propio condensador NMOS. Al eliminar el transporte lateral y la complejidad geométrica, puede examinarse directamente y sin ambigüedad el origen físico de la redistribución de carga y de la variación del potencial electrostático en el semiconductor.

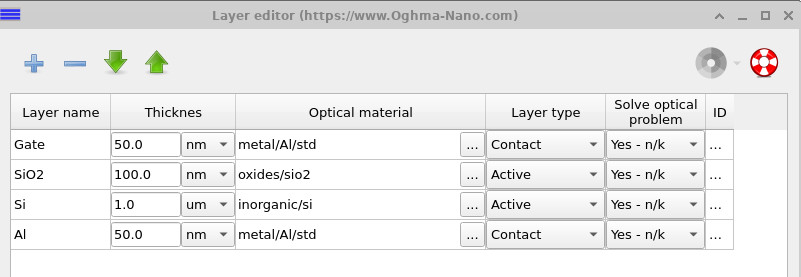

La estructura de capas puede inspeccionarse en el Editor de capas. Para mayor claridad, el espesor del óxido en este tutorial se ha elegido ligeramente mayor que en la tecnología moderna de silicio, de modo que la caída de potencial resultante, la capa de acumulación y la región de agotamiento sean claramente visibles en las gráficas de salida. En los condensadores NMOS contemporáneos, los espesores de óxido son típicamente del orden de 10 nm o menos. Después de completar el tutorial, se le anima a ajustar los espesores de capa y explorar cómo cambia la respuesta electrostática a medida que la estructura se aproxima a dimensiones realistas de dispositivo.

4. Inspeccionar la cinta eléctrica y la malla 2D

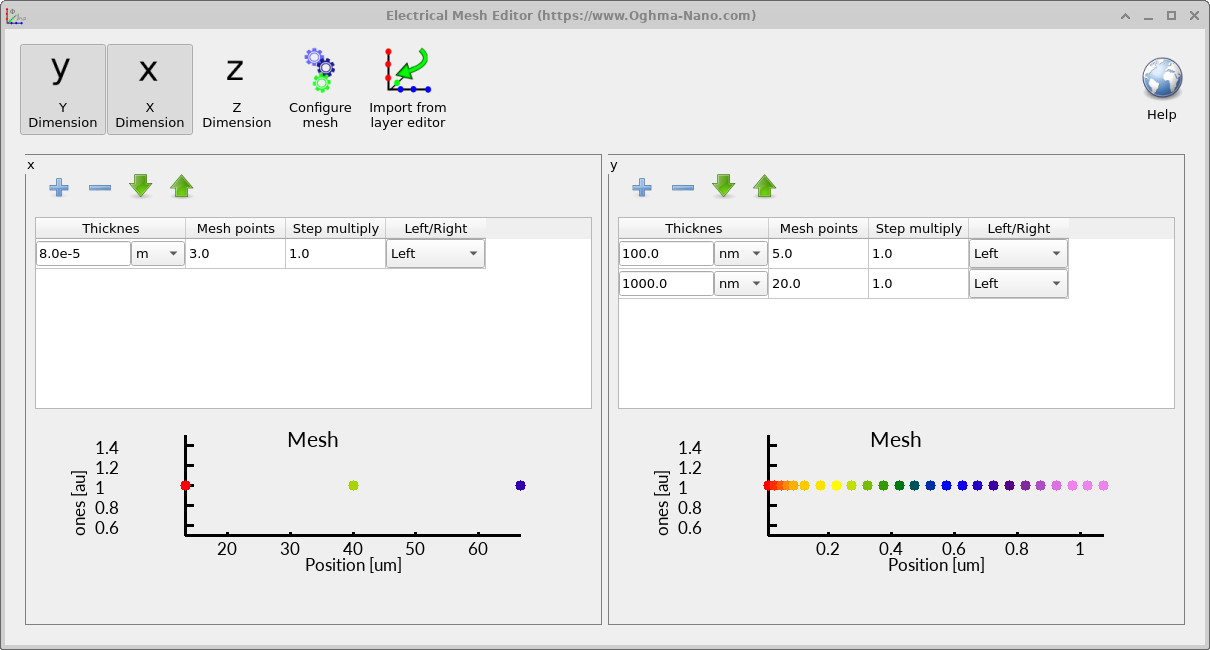

La mayor parte del flujo de trabajo del condensador NMOS se encuentra en la cinta Electrical. Desde aquí puede elegir qué modelo eléctrico está activo, editar parámetros, inspeccionar el dopado y configurar la malla. Al hacer clic en Electrical mesh se abre el editor de malla (véase ??).

Este tutorial utiliza una malla 2D: el dispositivo se resuelve en dos dimensiones para capturar la curvatura de bandas y el agotamiento cerca de la interfaz manteniendo tiempos de ejecución cortos. En el ejemplo mostrado, solo hay unos pocos puntos a lo largo de una dirección (lateral) y un muestreo más denso a través del espesor del óxido y del silicio (vertical), donde viven los gradientes electrostáticos. Puede aumentar el número de puntos de malla, pero el coste computacional aumenta aproximadamente con el número de incógnitas (y, para problemas no lineales, con el número de iteraciones por punto de polarización).

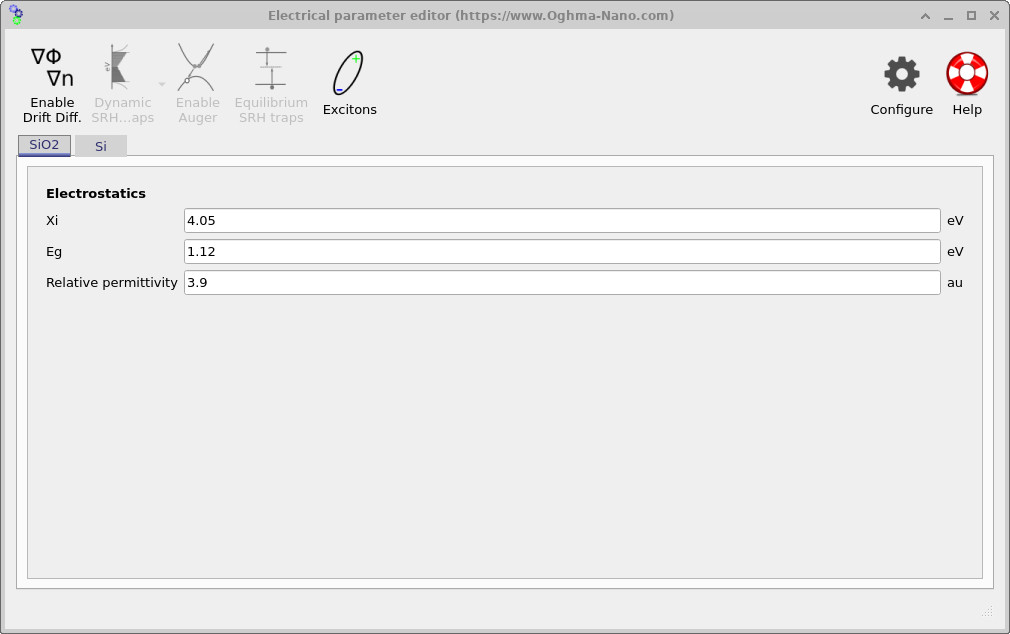

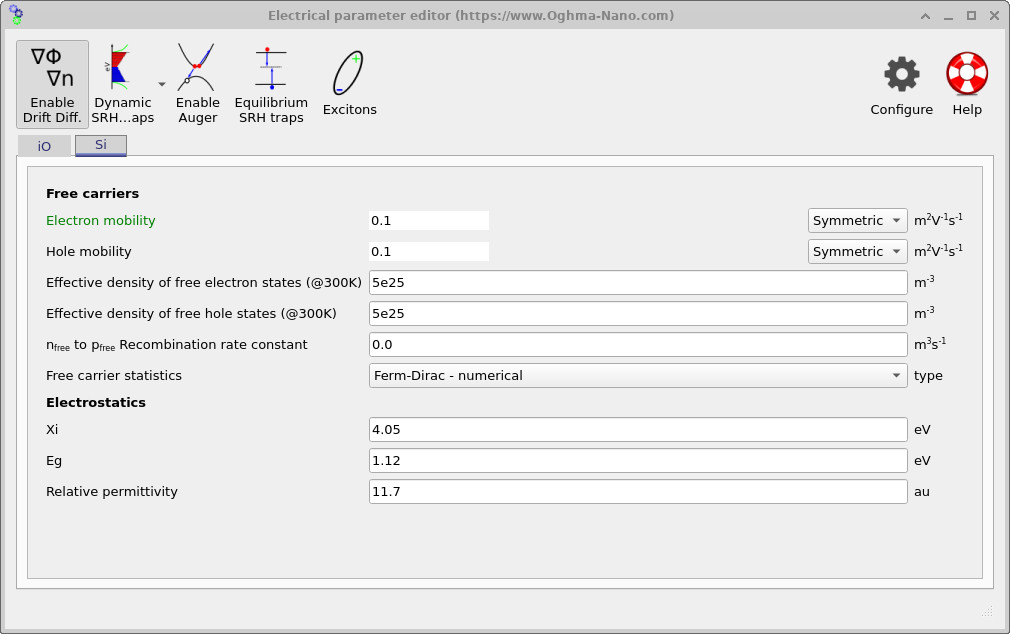

5. Editor de parámetros eléctricos (óxido frente a silicio)

Al hacer clic en Electrical parameters se abre el Editor de parámetros eléctricos. Este editor está organizado por material: la pestaña SiO2 contiene los parámetros del óxido, mientras que la pestaña Si contiene los parámetros del silicio. Para la capa de silicio, utilizamos un conjunto de parámetros físicamente razonable: una permitividad relativa de aproximadamente 11.7, valores estándar del silicio para la afinidad electrónica y el gap de banda, movilidades finitas de electrones y huecos, y densidades efectivas de estados realistas. Es importante que seleccionemos estadística de Fermi–Dirac en lugar de estadística de Maxwell–Boltzmann, ya que bajo polarización de compuerta la densidad de portadores cerca de la interfaz Si/SiO2 puede llegar a ser lo suficientemente alta como para que los efectos de degeneración sean importantes.

Para la capa de óxido, por el contrario, el único parámetro que desempeña un papel central en este tutorial es la permitividad relativa. El SiO2 se trata como un aislante ideal: soporta un campo eléctrico y una caída de voltaje, pero no soporta carga móvil. Como resultado, el comportamiento electrostático del condensador NMOS está gobernado por cómo se divide el voltaje de compuerta aplicado entre el óxido y el silicio, lo cual viene determinado enteramente por el espesor y la permitividad del óxido.

Esta elección de modelado se refleja en los botones de la parte superior del editor. En la capa SiO2, drift–diffusion está deshabilitado, por lo que allí solo se resuelve la ecuación de Poisson. En cambio, en la capa de silicio, drift–diffusion está habilitado para que pueda capturarse correctamente la redistribución de electrones y huecos en respuesta a la polarización de compuerta. Esta separación refleja los papeles físicos de los dos materiales en un condensador NMOS: el óxido media el campo eléctrico, mientras que el silicio alberga los portadores móviles.

Puede notar que parámetros como la afinidad electrónica y el gap de banda listados para SiO2 parecen similares a los del silicio. En el contexto de este tutorial, eso es intencional e inocuo. Dado que las ecuaciones de transporte de portadores no se resuelven en el óxido, estos parámetros de banda no influyen en la solución: no existe mecanismo para que electrones o huecos entren en el óxido en el modelo. Por tanto, el SiO2 participa solo a través de su respuesta dieléctrica, no a través de su estructura electrónica de bandas.

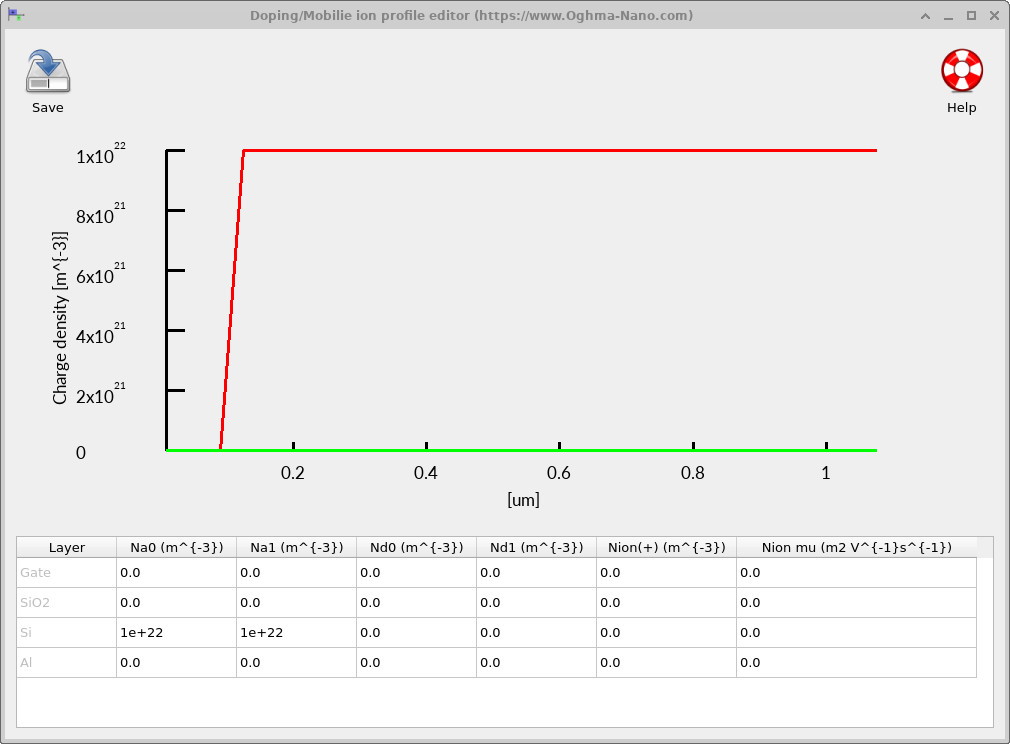

6. Editor de dopado (perfil de dopado del sustrato)

Por último, abra el editor de Doping desde la cinta Electrical para inspeccionar la distribución de dopantes (véase ??). Para un condensador NMOS, el sustrato de silicio es típicamente tipo p (dopado con aceptores). A polarización de compuerta nula o negativa, los huecos son los portadores mayoritarios cerca de la interfaz Si/SiO2. A medida que la polarización de compuerta se vuelve positiva, el campo eléctrico de compuerta repele huecos de la superficie, dejando atrás aceptores ionizados (carga negativa fija) y formando una región de agotamiento.

La concentración de dopantes controla fuertemente la respuesta electrostática del condensador. Un dopado tipo p más fuerte da lugar a una región de agotamiento más delgada para un potencial superficial dado, mientras que un dopado más ligero produce una región de agotamiento más ancha y una mayor extensión espacial de la curvatura de bandas. En la Parte B utilizaremos este editor para modificar deliberadamente el dopado del sustrato y observar los cambios resultantes en el ancho de agotamiento, el potencial electrostático y la estructura de bandas.

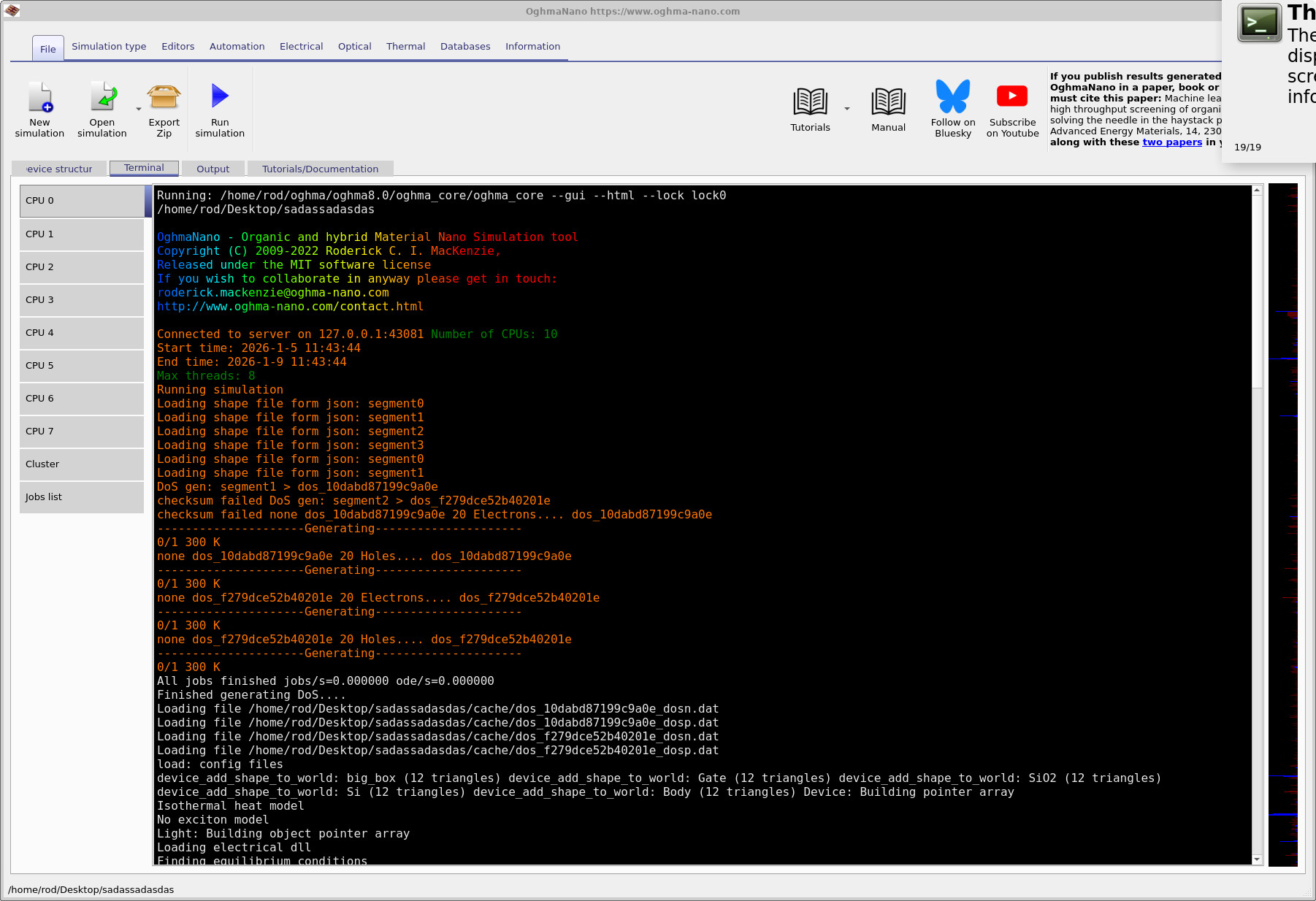

7. Ejecutar la simulación (salida del Terminal)

Haga clic en Run simulation (la flecha azul) en la ventana principal. OghmaNano cambiará a la pestaña Terminal y comenzará a ejecutar el solucionador. La primera etapa de una ejecución típica se muestra en ??, donde puede ver la línea de comandos utilizada para lanzar el solucionador principal, seguida de la carga del proyecto y la inicialización del modelo. Las líneas repetidas Generating... indican que OghmaNano está construyendo tablas de consulta para la estadística de Fermi–Dirac (para electrones y huecos en las capas que seleccionó). Evaluar con precisión las integrales de Fermi–Dirac es costoso, por lo que el código tabula estas cantidades una vez y luego las reutiliza durante las iteraciones no lineales. Cuando vea Loading file, está recargando las tablas en caché (u otros datos intermedios almacenados en caché) para evitar regenerarlas en cada ejecución.

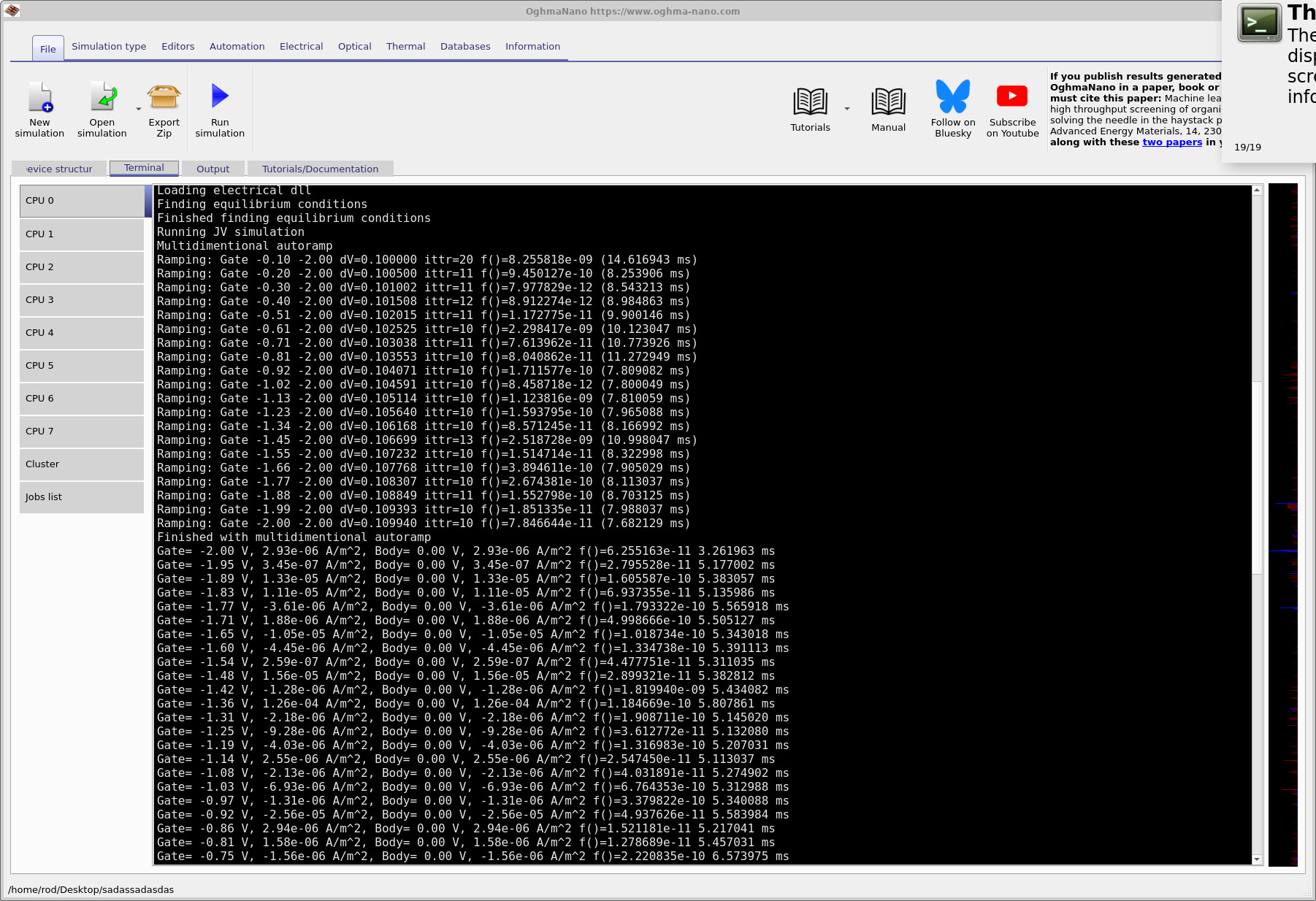

Una segunda etapa clave es la rampa de polarización. Antes de que comience el barrido principal, el solucionador lleva gradualmente la compuerta desde un punto de partida conocido y fácil (típicamente cerca del equilibrio) hasta el primer punto de polarización solicitado (aquí, hasta -2 V). Esta es una estrategia de continuación: los solucionadores de tipo Newton convergen de forma fiable solo cuando la estimación inicial está razonablemente cerca de la solución. Saltar directamente a una polarización grande puede colocar la estimación inicial “demasiado lejos”, provocando divergencia o una convergencia lenta e inestable. Al escalonar el voltaje de compuerta en pequeños incrementos, cada solución proporciona una buena estimación inicial para la siguiente.

Una vez que la compuerta ha alcanzado el voltaje inicial, el solucionador procede con el barrido de compuerta (la curva “J–V”/polarización). El cuerpo del dispositivo se mantiene a 0 V (como se informa en el terminal). Puede notar que la densidad de corriente impresa fluctúa en signo y magnitud aunque un condensador debería tener una corriente continua DC (esencialmente) nula. Ese comportamiento es normal aquí: el solucionador está informando corrientes residuales muy pequeñas cerca del suelo de ruido numérico de la resolución no lineal. En otras palabras, la “irregularidad” no es una corriente DC física; es un síntoma de intentar calcular una magnitud que es realmente ~0 con alta precisión relativa.

La magnitud informada como f(...)= es la medida de error/residuo no lineal (una métrica de convergencia). Cuando este valor es muy pequeño,

la solución electrostática (potencial, carga, curvatura de bandas) se considera convergida. El tiempo mostrado a la derecha (en milisegundos) es el

tiempo de ejecución por paso de polarización / bloque de iteración, y es útil para perfilar y para estimar el coste de aumentar la densidad de malla.

f(...) es el residuo del solucionador (métrica de convergencia).

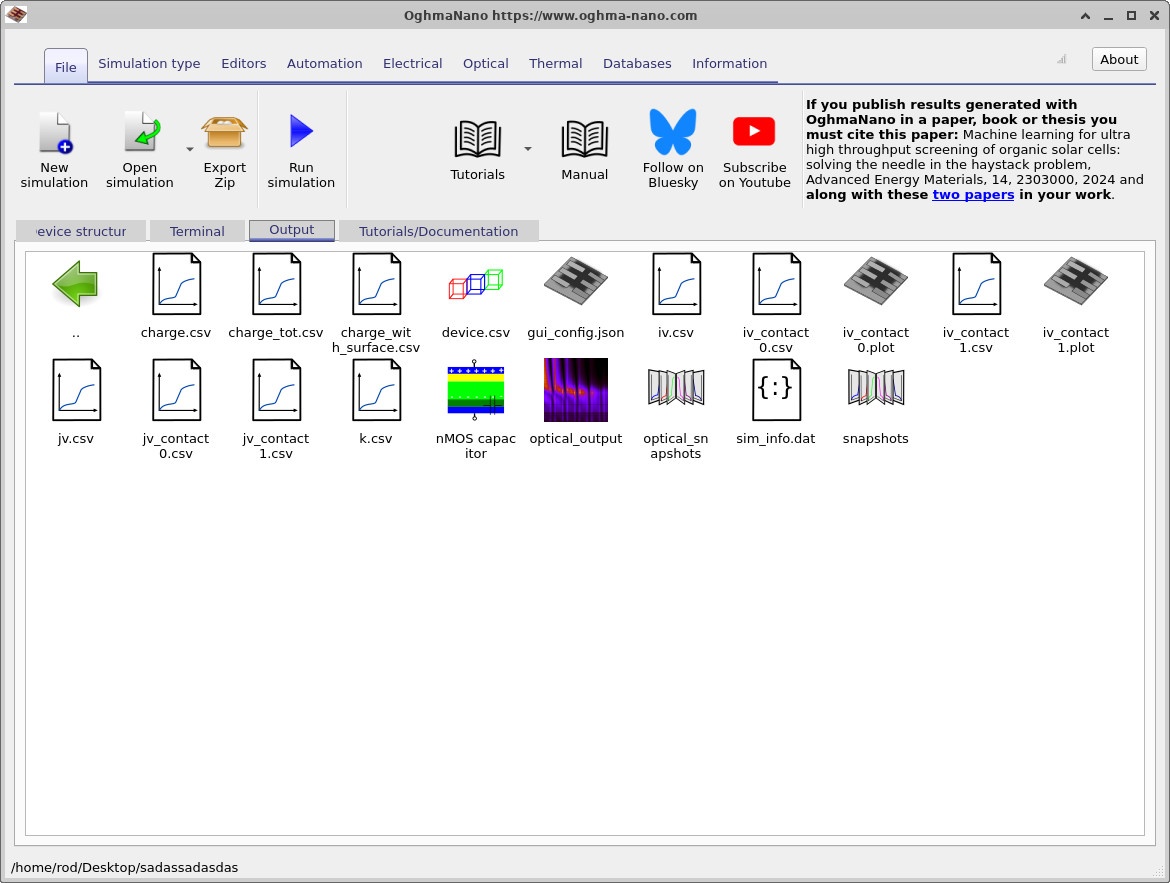

8. Archivos de salida y corriente de contacto

Cuando la ejecución finalice, cambie a la pestaña Output para ver los archivos producidos por la simulación

(véase ??).

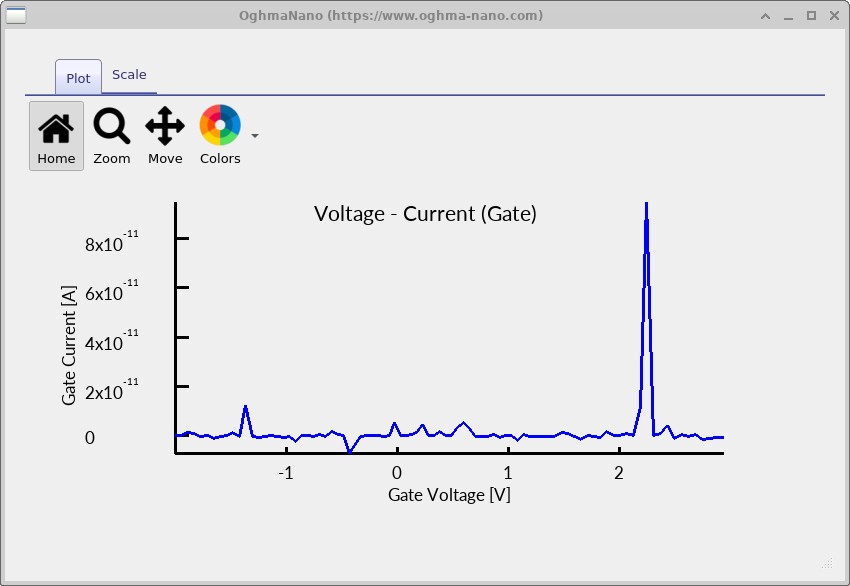

Puede hacer doble clic en entradas como iv_contact_0.csv y iv_contact_1.csv para abrir las gráficas de corriente de contacto.

Para un condensador MOS ideal, la corriente continua DC en estado estacionario es esencialmente nula, ya que la estructura es puramente electrostática. Las gráficas de corriente de contacto se incluyen por tanto principalmente como información de fondo y completitud, y como una comprobación sencilla de que no existen trayectorias de corriente no deseadas. Las curvas deben permanecer cerca de cero a lo largo del barrido de polarización; pequeñas fluctuaciones son normales y simplemente reflejan el hecho de que la corriente real es extremadamente pequeña.

En la siguiente sección iremos más allá de estas salidas auxiliares y nos centraremos en los resultados físicamente significativos de la simulación: el potencial electrostático, los bordes de banda, los niveles de Fermi y las distribuciones de portadores dentro del condensador NMOS.

💡 Lo que ha aprendido hasta ahora: En este tutorial configuró e inspeccionó una simulación de condensador NMOS (estructura del dispositivo, malla, parámetros de material y dopado). En Parte B seguimos a partir de esto aplicando polarización de compuerta e interpretando la salida de la simulación: curvatura de bandas, potencial electrostático, densidades de portadores y agotamiento superficial.