NMOS 커패시터 튜토리얼 (파트 A): 2D에서의 정전기와 공핍

1. 소개

MOSFET (Metal–Oxide–Semiconductor Field-Effect Transistor)은 게이트 전압을 사용하여 반도체 표면의 캐리어 밀도를 정전기적으로 제어함으로써 동작합니다. MOSFET 물리의 가장 단순한 “원자”는 MOS 커패시터입니다: 금속 게이트, 절연 산화막, 그리고 도핑된 반도체. MOS 커패시터를 이해하면, MOSFET이 스위칭하는 정전기를 이해하게 됩니다 (참조 ??).

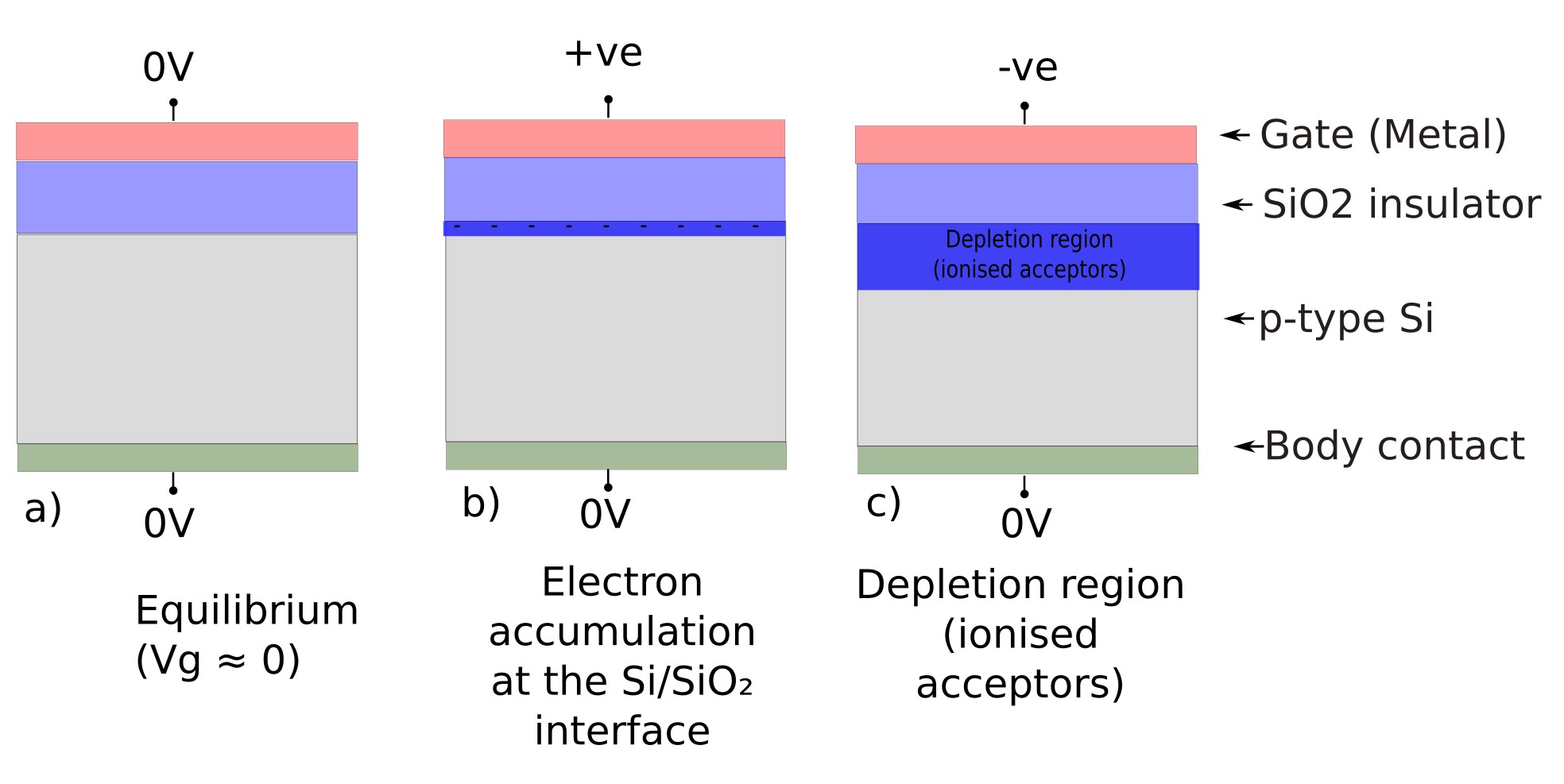

NMOS 장치는 트랜지스터 기하에서 켜졌을 때 n형 반전 채널을 형성하기 때문에 “NMOS”라고 불립니다—전도 채널 캐리어는 전자입니다. 실제로 이것은 일반적으로 p형 실리콘 바디(억셉터 도핑된 Si)와 충분히 양의 게이트 바이어스로 구현됩니다. 소스와 드레인을 도입하기 전에도, 동일한 게이트 정전기는 MOS 커패시터에서 보입니다: 양의 게이트 바이어스는 전자를 Si/SiO2 계면으로 끌어당기고(표면 축적), 음의 게이트 바이어스는 정공을 밀어내어 고정된 이온화 억셉터의 영역을 남기며 (공핍), 이는 ??에 나와 있습니다.

PMOS 장치는 상보적인 경우입니다: p형 채널을 형성하며 (정공이 전도 캐리어), 일반적으로 음의 게이트 바이어스 하에서 n형 바디를 사용합니다. NMOS/PMOS는 함께 CMOS 논리에 사용되는 기본 상보 쌍을 형성합니다.

이 튜토리얼에서는 OghmaNano에서 2D NMOS 커패시터 구조를 구축하고 탐색합니다. 우리는 의도적으로 축적 및 공핍 영역에 초점을 맞추며, 여기서는 물리가 정전기에 의해 지배되고 결과가 해석하기 쉽습니다. 강한 반전(진정한 전도 채널)은 파트 B 및 이후 튜토리얼로 미룹니다.

2. OghmaNano 실행

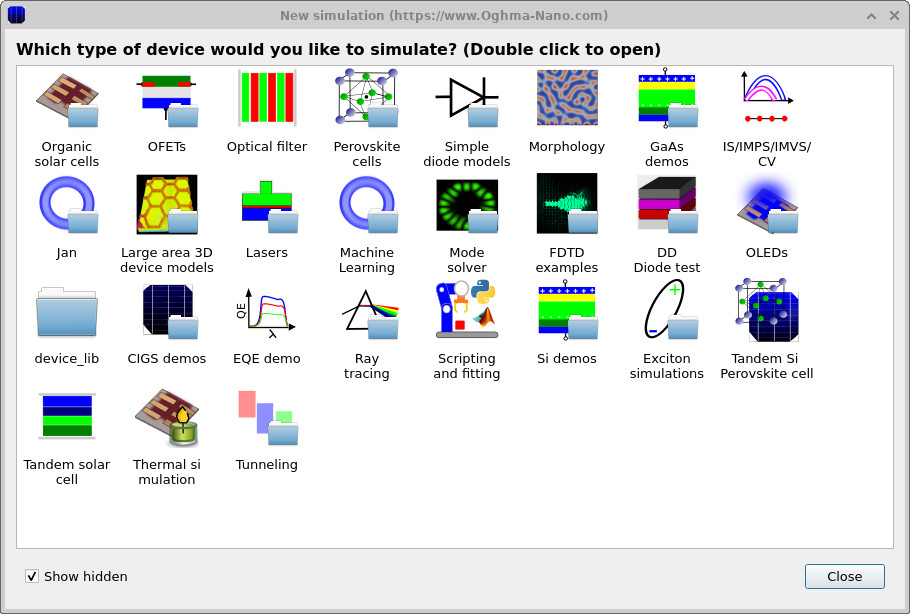

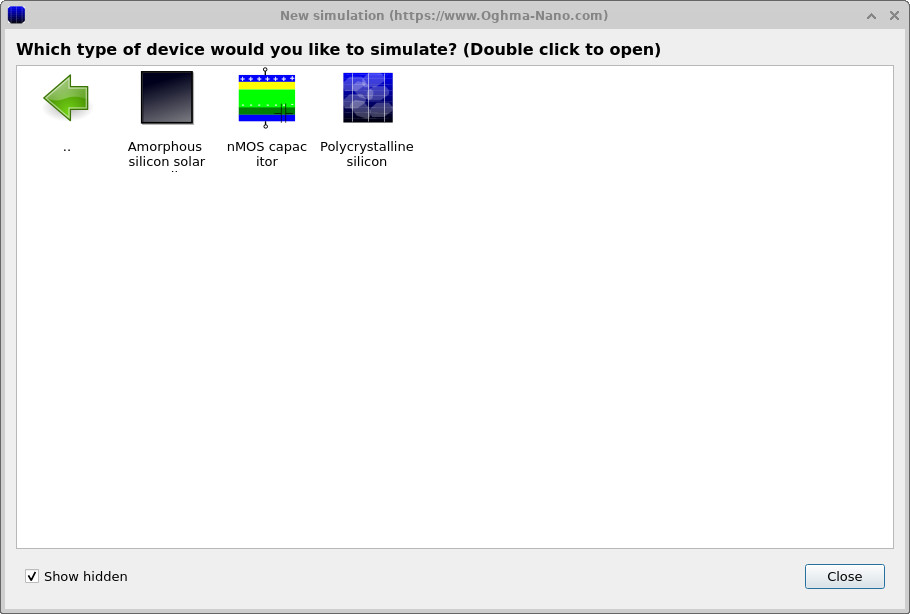

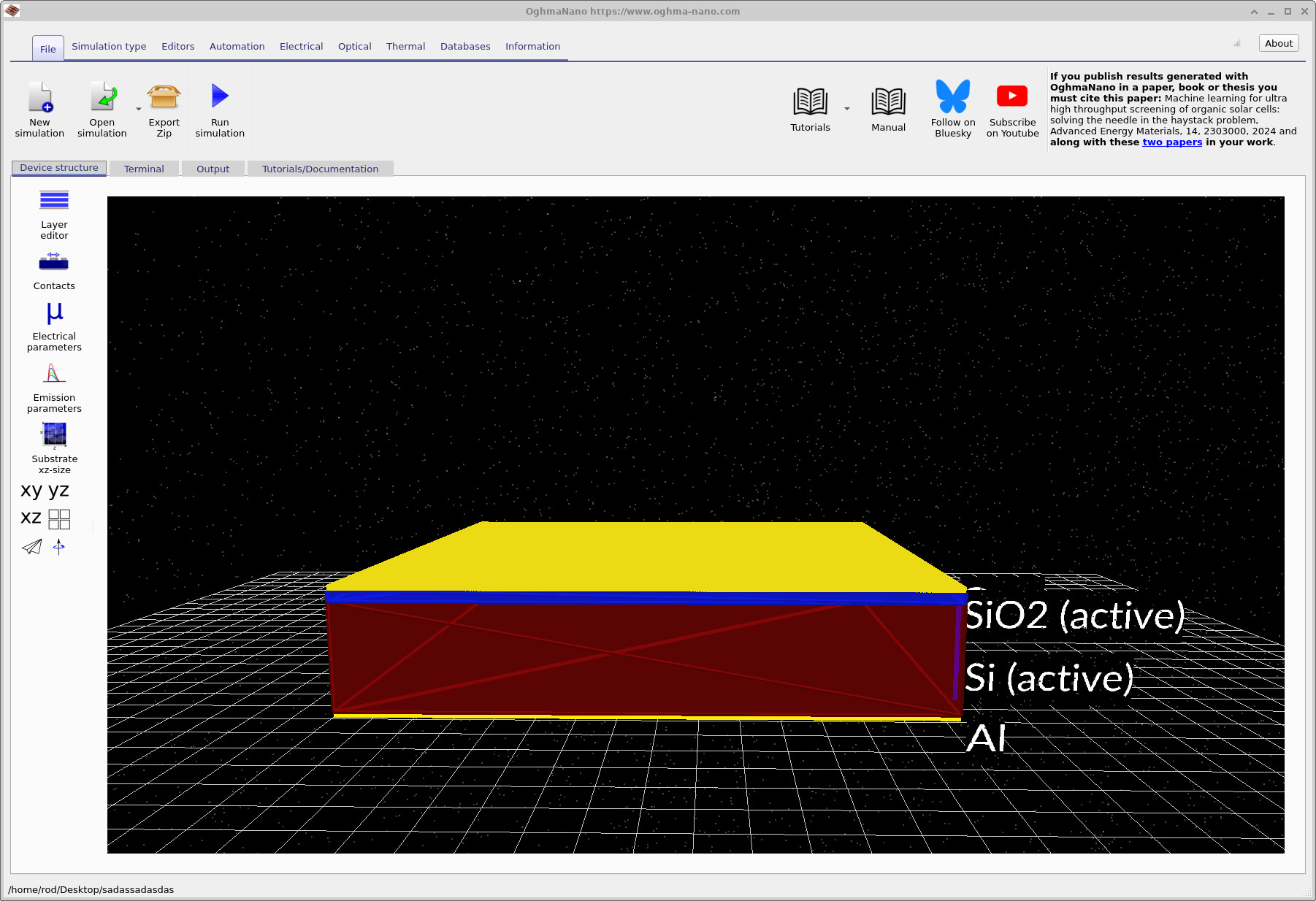

Windows 시작 메뉴에서 OghmaNano를 실행합니다. OghmaNano 메인 창이 ??와 같이 나타납니다. New simulation을 클릭합니다. 그러면 사용 가능한 장치 유형 라이브러리가 열리며, 이는 ??에 나와 있습니다. Si demos를 더블클릭하여 실리콘 예제 세트를 연 다음, ??에 표시된 것처럼 nMOS capacitor 예제를 선택합니다. 메시지가 나타나면 쓰기 권한이 있는 로컬 폴더에 시뮬레이션을 저장합니다. 저장 후 메인 시뮬레이션 창이 열립니다 (참조 ??).

💡 팁: 최상의 성능을 위해 시뮬레이션은 로컬 드라이브(예: C:\)에 저장하십시오.

네트워크 또는 클라우드 동기화 폴더에서는 반복적인 솔버 실행이 느려질 수 있습니다.

3. 장치 구조 확인 (층과 재료)

프로젝트를 만든 후 메인 시뮬레이션 창이 열리며, 여기에는 의도적으로 단순화된 NMOS MOS 커패시터 구조가 표시됩니다: 금속 게이트, SiO2 게이트 산화막, 그리고 p형 실리콘 기판과 바디 접촉입니다. 이는 반도체 바디가 p형이고, 양의 게이트 바이어스가 표면 정전기를 전자 축적 방향으로 유도하기 때문에 NMOS 커패시터라고 불립니다. 이 구조는 전형적인 NMOS 정전기 구성을 나타내며 Si/SiO2 계면에서의 밴드 벤딩, 축적 및 공핍을 연구하는 데 널리 사용됩니다.

실제 장치에서는 MOS 커패시터가 더 복잡한 레이아웃에 포함되거나 추가 접촉과 결합되는 경우가 많습니다. 여기서는 그러한 요소들을 의도적으로 생략하여 초점을 NMOS 커패시터 자체의 수직 정전기에만 맞춥니다. 측면 수송과 기하학적 복잡성을 제거함으로써, 반도체 내 전하 재분포와 정전위 변화의 물리적 기원을 직접적이고 모호함 없이 조사할 수 있습니다.

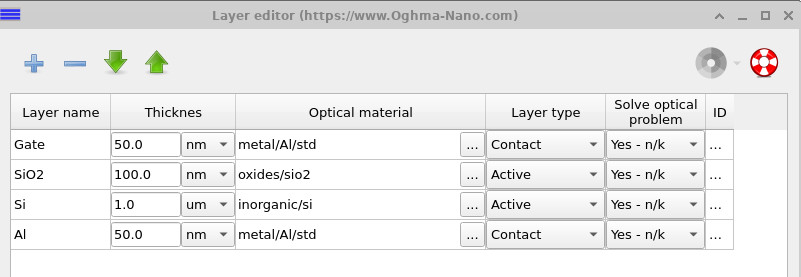

층 구조는 Layer editor에서 확인할 수 있습니다. 명확성을 위해, 이 튜토리얼의 산화막 두께는 현대 실리콘 기술보다 약간 더 크게 선택되어, 결과 출력 플롯에서 전위 강하, 축적층 및 공핍 영역이 분명하게 보이도록 했습니다. 현대 NMOS 커패시터에서 산화막 두께는 일반적으로 10 nm 이하입니다. 튜토리얼을 마친 후에는 층 두께를 조정하여 구조가 실제 장치 차원에 가까워질 때 정전기 응답이 어떻게 변하는지 탐색해 보시기 바랍니다.

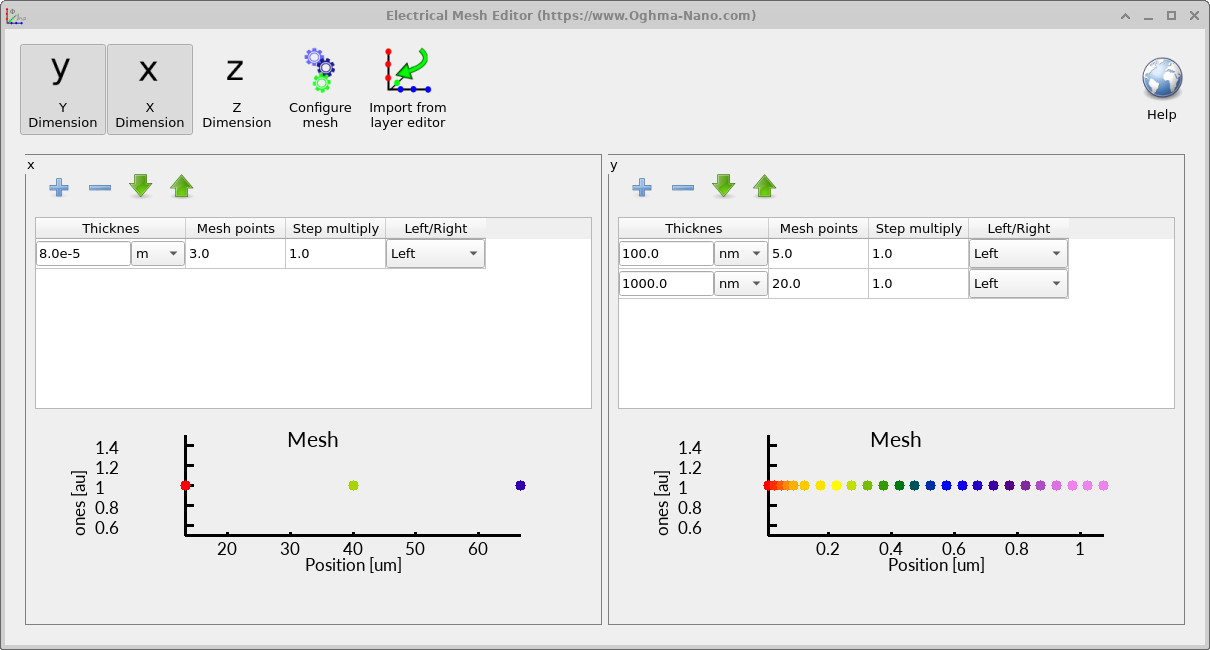

4. 전기 리본과 2D 메쉬 확인

NMOS 커패시터 워크플로의 대부분은 Electrical 리본에 있습니다. 여기서 활성 전기 모델을 선택하고, 매개변수를 편집하고, 도핑을 확인하고, 메쉬를 구성할 수 있습니다. Electrical mesh를 클릭하면 메쉬 편집기가 열립니다 (참조 ??).

이 튜토리얼은 2D 메쉬를 사용합니다: 장치는 두 차원에서 분해되어 계면 근처의 밴드 벤딩과 공핍을 포착하면서도 실행 시간은 짧게 유지합니다. 표시된 예제에서는 한 방향(측면)으로는 몇 개의 점만 있고, 산화막과 실리콘 두께 방향(수직)으로는 더 촘촘한 샘플링이 있습니다. 이곳에 정전기 기울기가 존재합니다. 메쉬 점 수를 늘릴 수는 있지만, 계산 비용은 대략 미지수 수에 따라 증가합니다 (그리고 비선형 문제의 경우, 바이어스 점당 반복 횟수에도 비례).

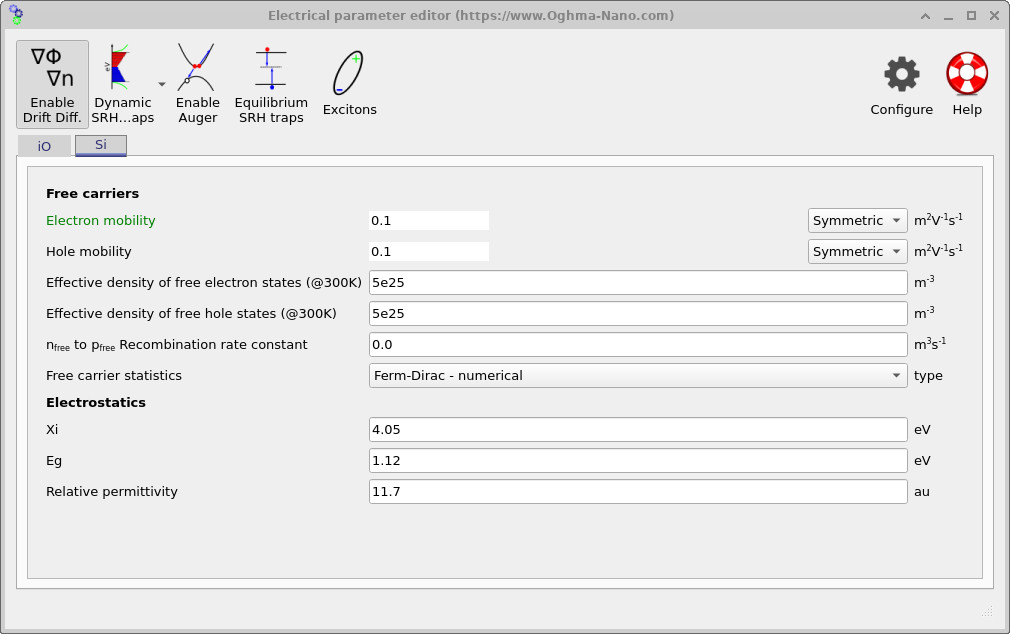

5. Electrical Parameter Editor (산화막 대 실리콘)

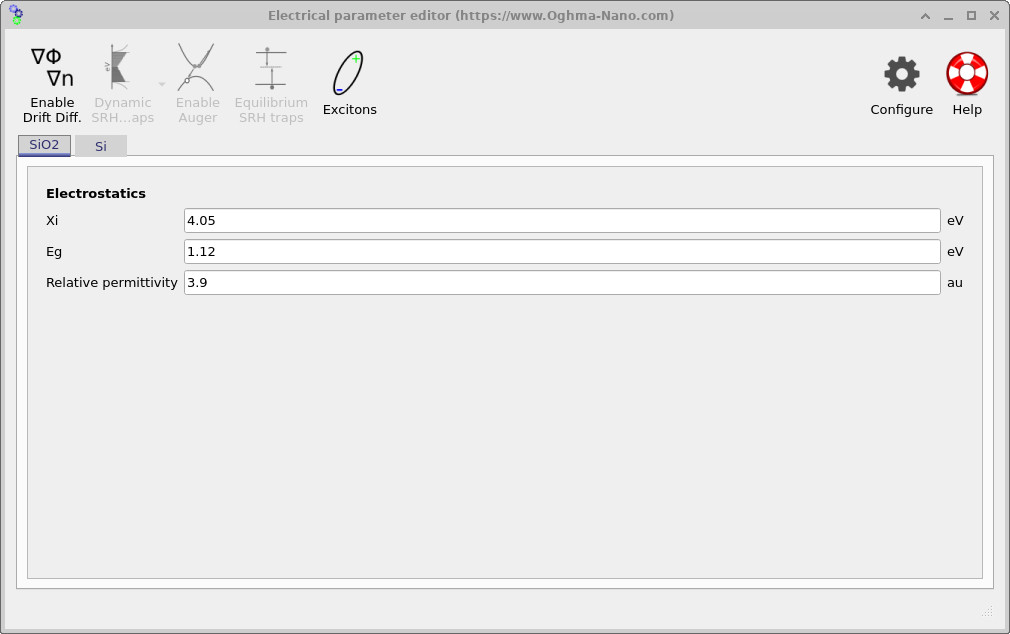

Electrical parameters를 클릭하면 Electrical Parameter Editor가 열립니다. 이 편집기는 재료별로 구성됩니다: SiO2 탭에는 산화막 매개변수가, Si 탭에는 실리콘 매개변수가 있습니다. 실리콘 층에는 물리적으로 타당한 매개변수 세트를 사용합니다: 상대 유전율은 약 11.7, 전자 친화도와 밴드갭은 표준 실리콘 값, 유한한 전자 및 정공 이동도, 그리고 현실적인 유효 상태 밀도입니다. 중요한 점은 Maxwell–Boltzmann 통계가 아니라 Fermi–Dirac 통계를 선택한다는 것입니다. 이는 게이트 바이어스 하에서 Si/SiO2 계면 근처의 캐리어 밀도가 충분히 높아져 축퇴 효과가 중요해질 수 있기 때문입니다.

반면 산화막 층에서는 이 튜토리얼에서 중심적인 역할을 하는 매개변수는 상대 유전율뿐입니다. SiO2는 이상적인 절연체로 취급됩니다: 전기장과 전압 강하는 지지하지만, 이동 전하를 지지하지는 않습니다. 따라서 NMOS 커패시터의 정전기 거동은 인가된 게이트 전압이 산화막과 실리콘 사이에서 어떻게 분배되는지에 의해 결정되며, 이는 오직 산화막 두께와 유전율에 의해 정해집니다.

이 모델링 선택은 편집기 상단의 버튼들에 반영되어 있습니다. SiO2 층에서는 drift–diffusion이 비활성화되어 있으므로, 그곳에서는 Poisson 방정식만 풉니다. 반면 실리콘 층에서는 drift–diffusion이 활성화되어 있으므로, 게이트 바이어스에 대한 전자와 정공의 재분포를 올바르게 포착할 수 있습니다. 이러한 분리는 NMOS 커패시터에서 두 재료의 물리적 역할을 반영합니다: 산화막은 전기장을 매개하고, 실리콘은 이동 캐리어를 수용합니다.

SiO2에 대해 나열된 전자 친화도와 밴드갭과 같은 매개변수가 실리콘의 값과 유사하게 보일 수 있습니다. 이 튜토리얼의 맥락에서는 이것이 의도된 것이며 문제되지 않습니다. 산화막에서는 캐리어 수송 방정식을 풀지 않기 때문에, 이러한 밴드 매개변수는 해에 영향을 주지 않습니다: 모델에서는 전자나 정공이 산화막으로 들어갈 메커니즘이 없습니다. 따라서 SiO2는 전자 밴드 구조가 아니라 유전 응답을 통해서만 참여합니다.

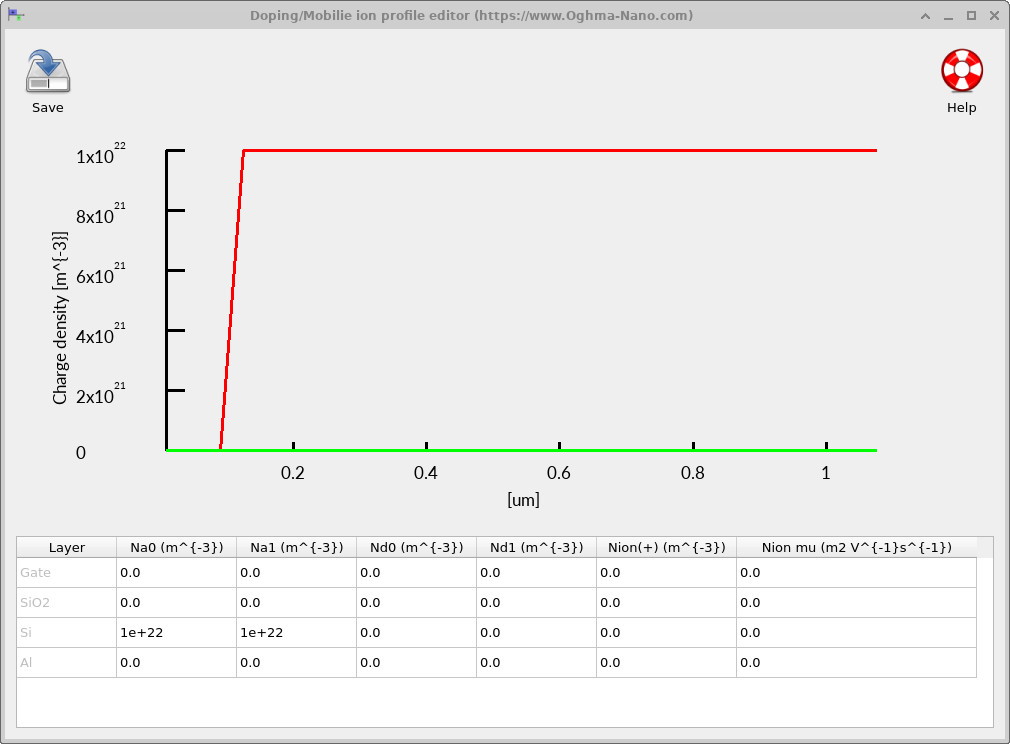

6. Doping editor (기판 도핑 프로파일)

마지막으로 Electrical 리본에서 Doping 편집기를 열어 도펀트 분포를 확인합니다 (참조 ??). NMOS 커패시터의 경우, 실리콘 기판은 일반적으로 p형 (억셉터 도핑)입니다. 0 또는 음의 게이트 바이어스에서는 정공이 Si/SiO2 계면 근처의 다수 캐리어입니다. 게이트 바이어스가 양으로 커질수록, 게이트 전기장은 표면에서 정공을 밀어내고, 그 결과 이온화 억셉터 (고정 음전하)가 남아 공핍 영역이 형성됩니다.

도펀트 농도는 커패시터의 정전기 응답을 강하게 제어합니다. 더 무거운 p형 도핑은 주어진 표면 전위에 대해 더 얇은 공핍 영역을 만들고, 더 가벼운 도핑은 더 넓은 공핍 영역과 더 큰 공간적 밴드 벤딩 범위를 만듭니다. 파트 B에서는 이 편집기를 사용하여 기판 도핑을 의도적으로 수정하고, 그 결과로 생기는 공핍 폭, 정전위 및 밴드 구조의 변화를 관찰할 것입니다.

7. 시뮬레이션 실행 (Terminal 출력)

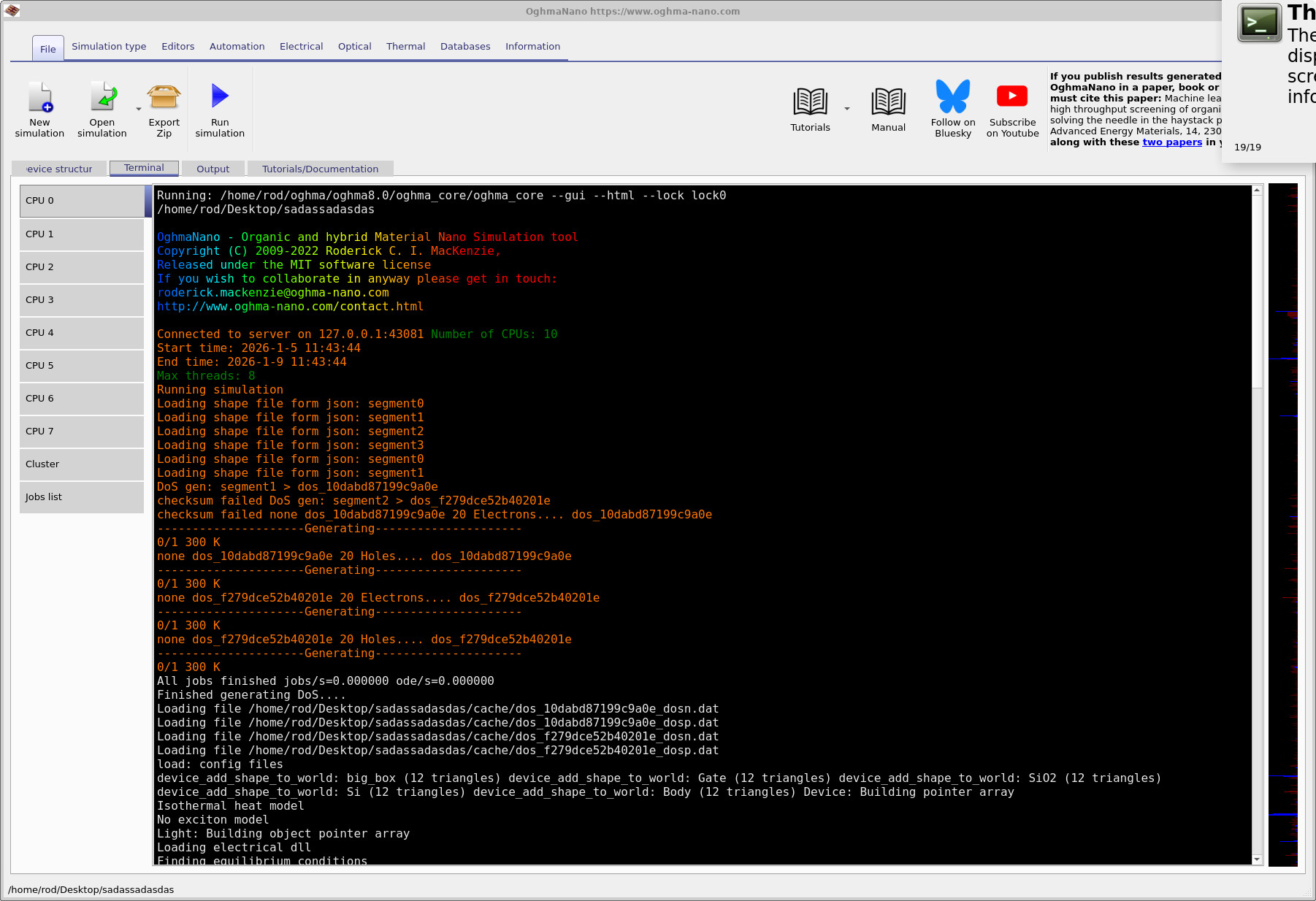

메인 창에서 Run simulation (파란 화살표)을 클릭합니다. OghmaNano는 Terminal 탭으로 전환하고 솔버 실행을 시작합니다. 일반적인 실행의 첫 번째 단계는 ??에 표시되어 있습니다. 여기서 코어 솔버를 실행하는 데 사용된 명령줄을 볼 수 있으며, 그 다음 프로젝트 로딩과 모델 초기화가 이어집니다. 반복되는 Generating... 줄은 OghmaNano가 Fermi–Dirac 통계용 lookup table을 구축하고 있음을 나타냅니다 (선택한 층의 전자와 정공에 대해). Fermi–Dirac 적분을 정확하게 평가하는 것은 비용이 크므로, 코드는 이러한 양을 한 번 표로 만든 다음 비선형 반복 동안 이를 재사용합니다. Loading file이 보이면, 이는 캐시된 테이블(또는 다른 캐시된 중간 데이터)을 다시 불러와 매번 재생성하지 않도록 하는 것입니다.

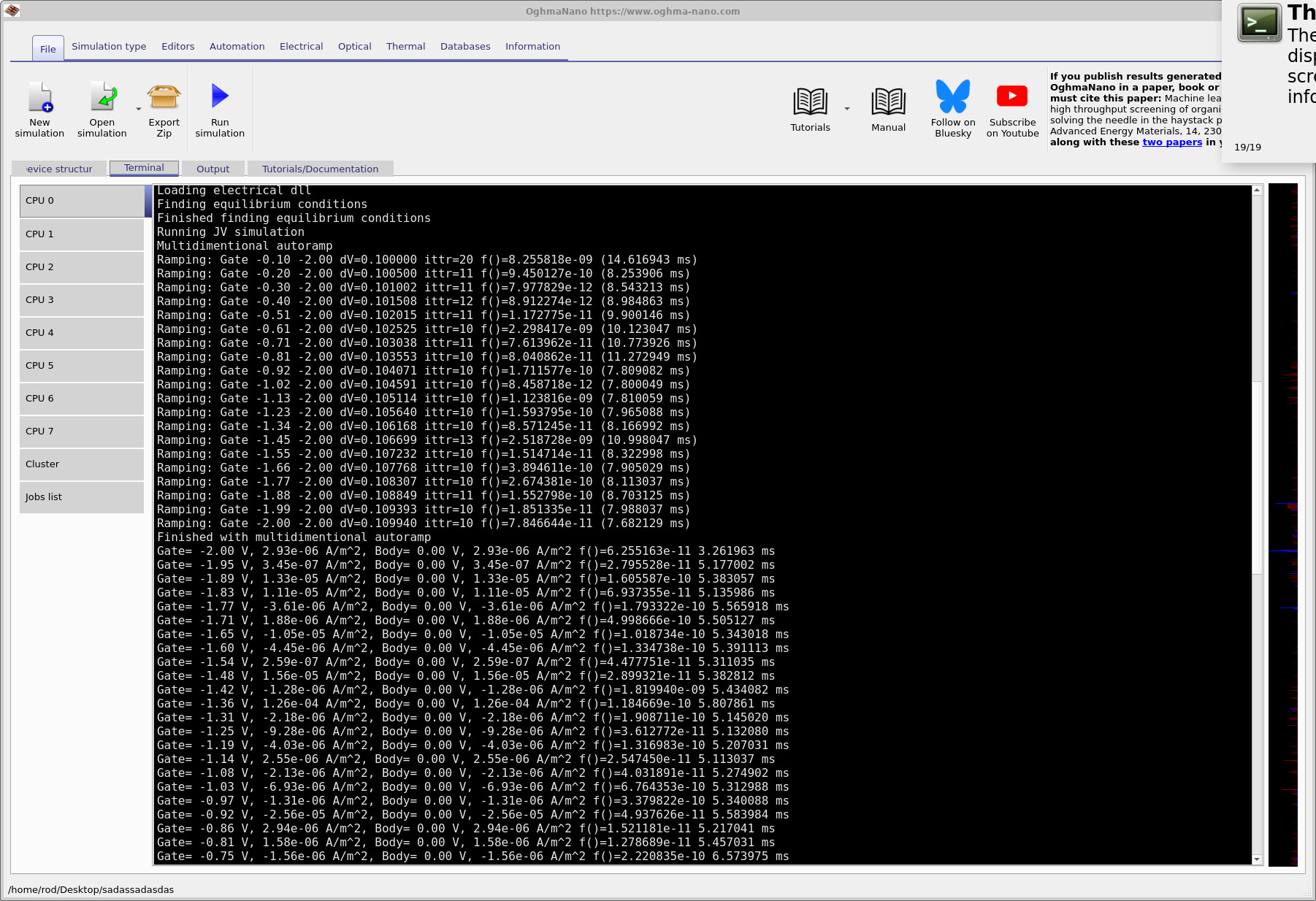

두 번째 핵심 단계는 바이어스 램핑입니다. 메인 스윕이 시작되기 전에, 솔버는 게이트를 알려져 있고 쉬운 시작점(일반적으로 평형 근처)에서 첫 번째 요청된 바이어스 점(여기서는 -2 V)까지 점진적으로 램프합니다. 이것은 continuation 전략입니다: Newton형 솔버는 초기 추정값이 해에 충분히 가까울 때만 안정적으로 수렴합니다. 큰 바이어스로 바로 점프하면 초기 추정값이 “너무 멀리” 있게 되어 발산하거나 느리고 불안정한 수렴을 초래할 수 있습니다. 게이트 전압을 작은 단계로 올리면, 각 해가 다음 해에 대한 좋은 초기 추정값을 제공합니다.

게이트가 시작 전압에 도달하면, 솔버는 게이트 스윕(“J–V”/바이어스 곡선)을 진행합니다. 장치 바디는 0 V에 고정됩니다 (터미널에 보고되는 대로). 커패시터는 (본질적으로) 정상 상태 DC 전류가 0이어야 하는데도, 출력되는 전류 밀도의 부호와 크기가 흔들리는 것을 볼 수 있습니다. 여기서는 그런 거동이 정상입니다: 솔버는 비선형 해의 수치 잡음 바닥 근처에 있는 매우 작은 잔류 전류를 보고하고 있습니다. 다시 말해, 그 “들쭉날쭉함”은 물리적인 DC 전류가 아니라, 실제로 ~0인 양을 높은 상대 정확도로 계산하려 할 때 나타나는 증상입니다.

f(...)=로 보고되는 양은 비선형 잔차/오차 척도(수렴 지표)입니다. 이 값이 매우 작으면,

정전기 해 (전위, 전하, 밴드 벤딩)는 수렴된 것으로 간주됩니다. 오른쪽에 표시되는 시간(밀리초)은

바이어스 스텝/반복 블록당 실행 시간이며, 메쉬 밀도 증가 비용을 판단하고 프로파일링하는 데 유용합니다.

f(...) 값은 솔버 잔차(수렴 지표)입니다.

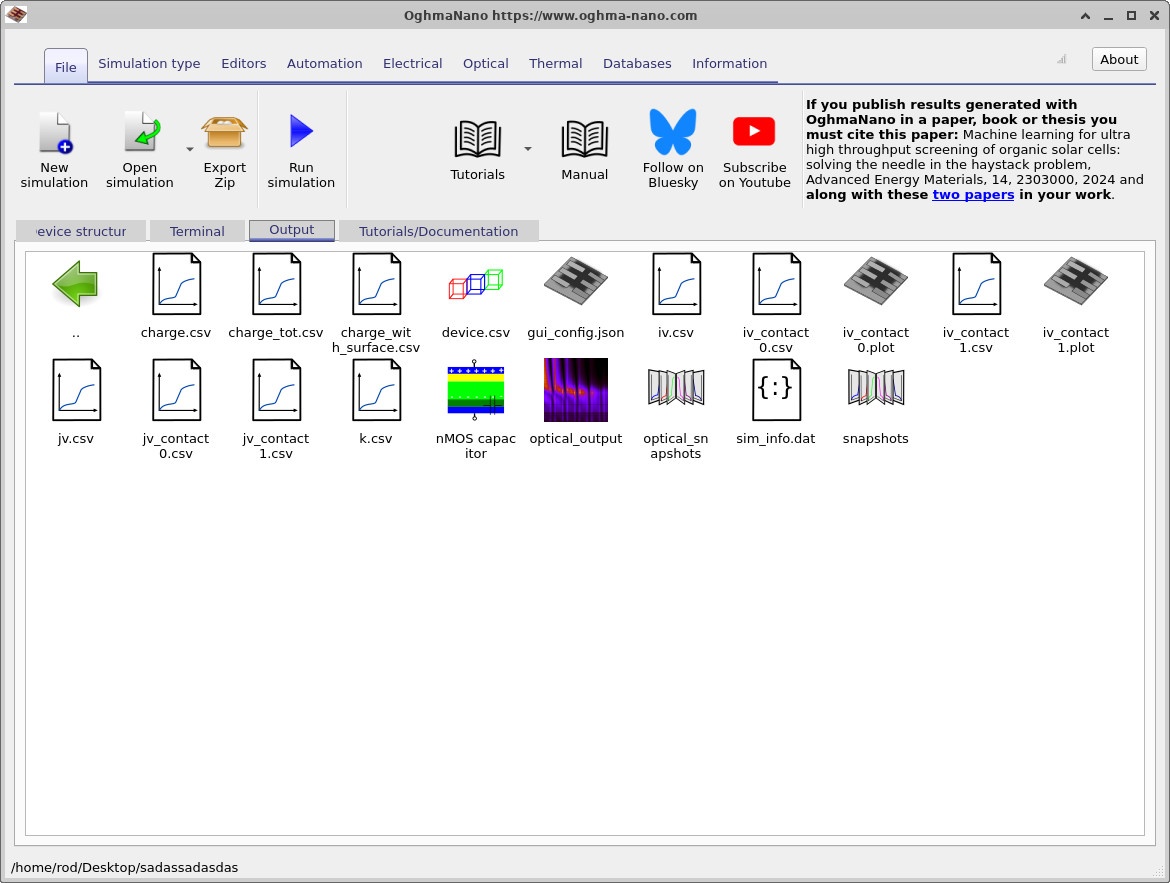

8. 출력 파일과 접촉 전류

실행이 완료되면 Output 탭으로 전환하여 시뮬레이션이 생성한 파일을 확인합니다

(참조 ??).

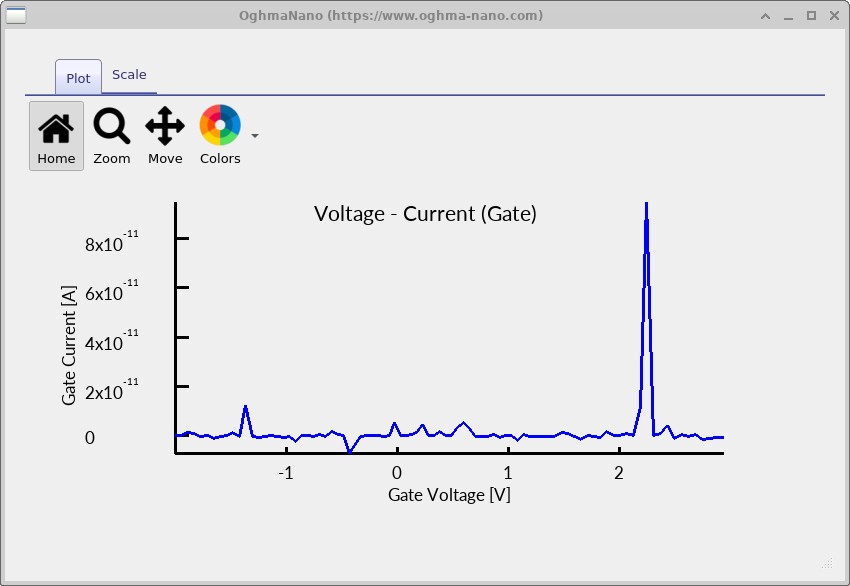

iv_contact_0.csv 및 iv_contact_1.csv와 같은 항목을 더블클릭하여 접촉 전류 플롯을 열 수 있습니다.

이상적인 MOS 커패시터에서는 구조가 순수하게 정전기적이므로 정상 상태 DC 전류는 본질적으로 0입니다. 따라서 접촉 전류 플롯은 주로 배경 정보와 완전성을 위해 포함되며, 의도하지 않은 전류 경로가 존재하지 않는지 확인하는 간단한 sanity check 역할을 합니다. 곡선은 바이어스 스윕 전반에 걸쳐 0에 가깝게 유지되어야 합니다; 작은 변동은 정상이며, 이는 실제 전류가 극히 작다는 사실을 단순히 반영합니다.

다음 섹션에서는 이러한 보조 출력에서 벗어나, NMOS 커패시터 내의 정전위, 밴드 에지, Fermi 준위 및 캐리어 분포와 같은 시뮬레이션의 물리적으로 의미 있는 결과에 집중할 것입니다.

💡 지금까지 배운 내용: 이 튜토리얼에서는 NMOS 커패시터 시뮬레이션을 설정하고 확인했습니다 (장치 구조, 메쉬, 재료 매개변수, 도핑). 파트 B에서는 여기에 기반하여 게이트 바이어스를 인가하고 시뮬레이션 출력—밴드 벤딩, 정전위, 캐리어 밀도, 표면 공핍—을 해석합니다.