NMOS 电容教程(Part B):能带弯曲、电荷与表面电势

1. 引言

在 Part A 中,我们重点介绍了如何建立并运行 2D NMOS 电容仿真。

在本节中,我们将转向对求解器输出的物理解读。

下方所示的所有图都来自仿真输出中的 snapshots 目录,

并对应于不同的栅极外加电压。

在整个分析过程中需要始终记住的关键点是,NMOS 电容由 静电学支配:外加栅压会重新分布硅中的电荷, 进而使能带弯曲,并决定 Si/SiO2 界面处的表面电势。

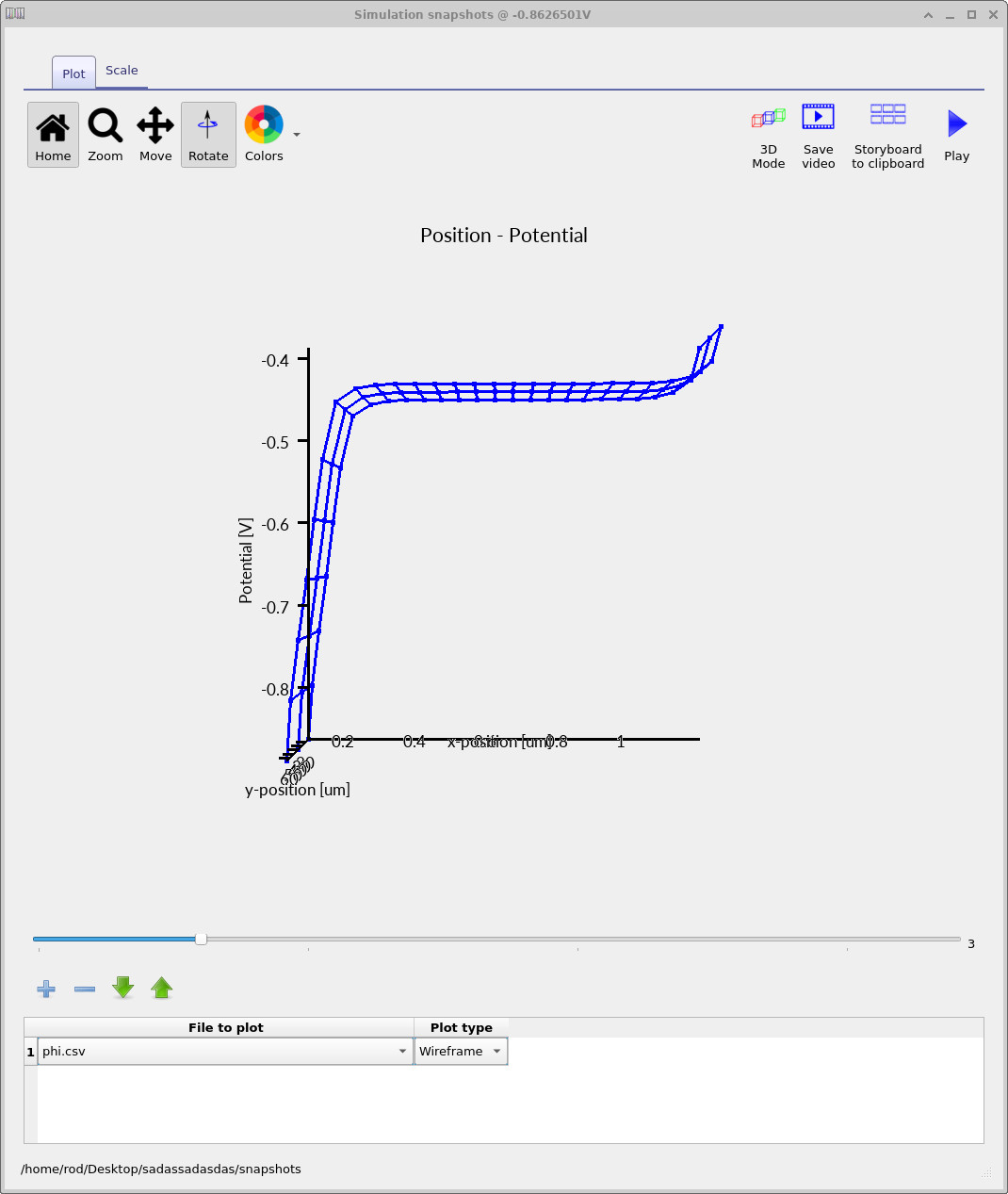

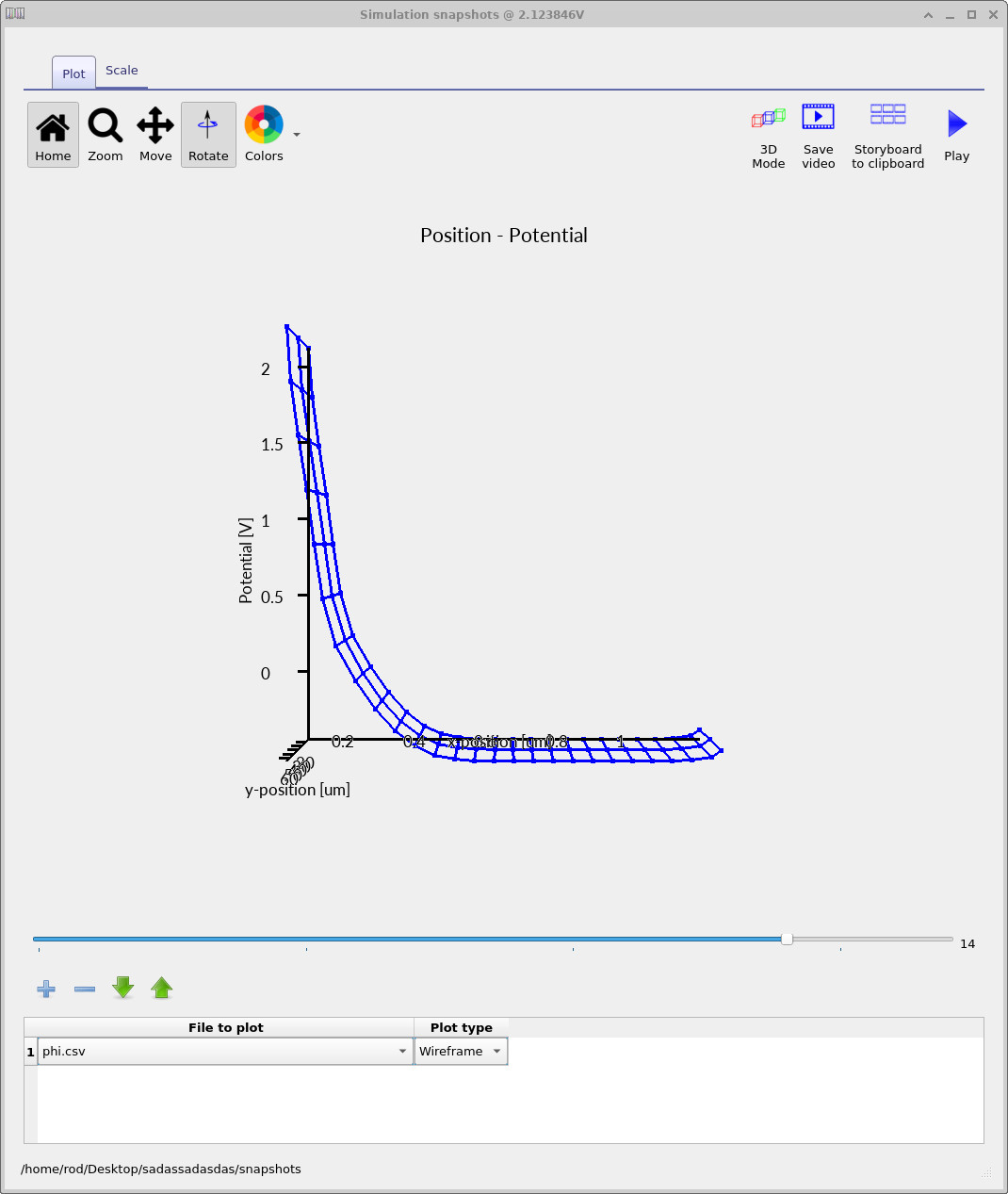

2. 静电势与表面电势

我们首先通过检查静电势

(phi.csv)来开始分析,它是 Poisson 方程求解的基本量。

电势直接显示外加栅压如何在

SiO2 氧化层和硅之间分配,因此它决定了控制后续所有能带弯曲的

静电边界条件。

在 NMOS 电容中,外加电压并不会在整个结构中均匀下降。 相反,氧化层和硅之间的电压分配由它们的 相对介电常数和厚度控制。 氧化层具有较低的介电常数,因此在一个较薄区域内承受较强电场, 而硅则通过形成一个空间电荷区来响应,其范围取决于偏压。 这些效应都可以直接从静电势分布中看出来。

静电势通过 snapshots 输出进行可视化。

仿真完成后,切换到 Output 选项卡

(见 ??),

然后双击 snapshots 目录以打开 snapshots 窗口。

在 snapshots 窗口中,点击蓝色加号图标以添加一个绘图条目,

然后使用 File to plot 列中的下拉菜单选择

phi.csv。

每一个曲面都对应于偏压扫描中某个不同栅压下的静电势。

滑动条允许你浏览这些电压,并探索电势如何随外加栅极偏压变化。

snapshots 目录以访问内部仿真变量,

如静电势和能带。

在负栅极偏压下,电势在氧化层中变化剧烈, 但在体硅中几乎保持常数。 这表明 p 型硅能够快速重排电荷以屏蔽外加电场, 从而使衬底深处只剩下很弱的电场。随着栅压变为正值, 硅将不再能够完全屏蔽电场。 在 Si/SiO2 界面附近会形成明显的电势梯度, 从而定义一个其宽度随栅压增加而扩展的耗尽区。 这个表面电势正是决定能带如何弯曲的关键量。

在下一节中,我们将检查导带和价带边缘。 这些能带分布并不会引入新的物理过程;它们只是前面分析过的 静电势分布的直接结果。

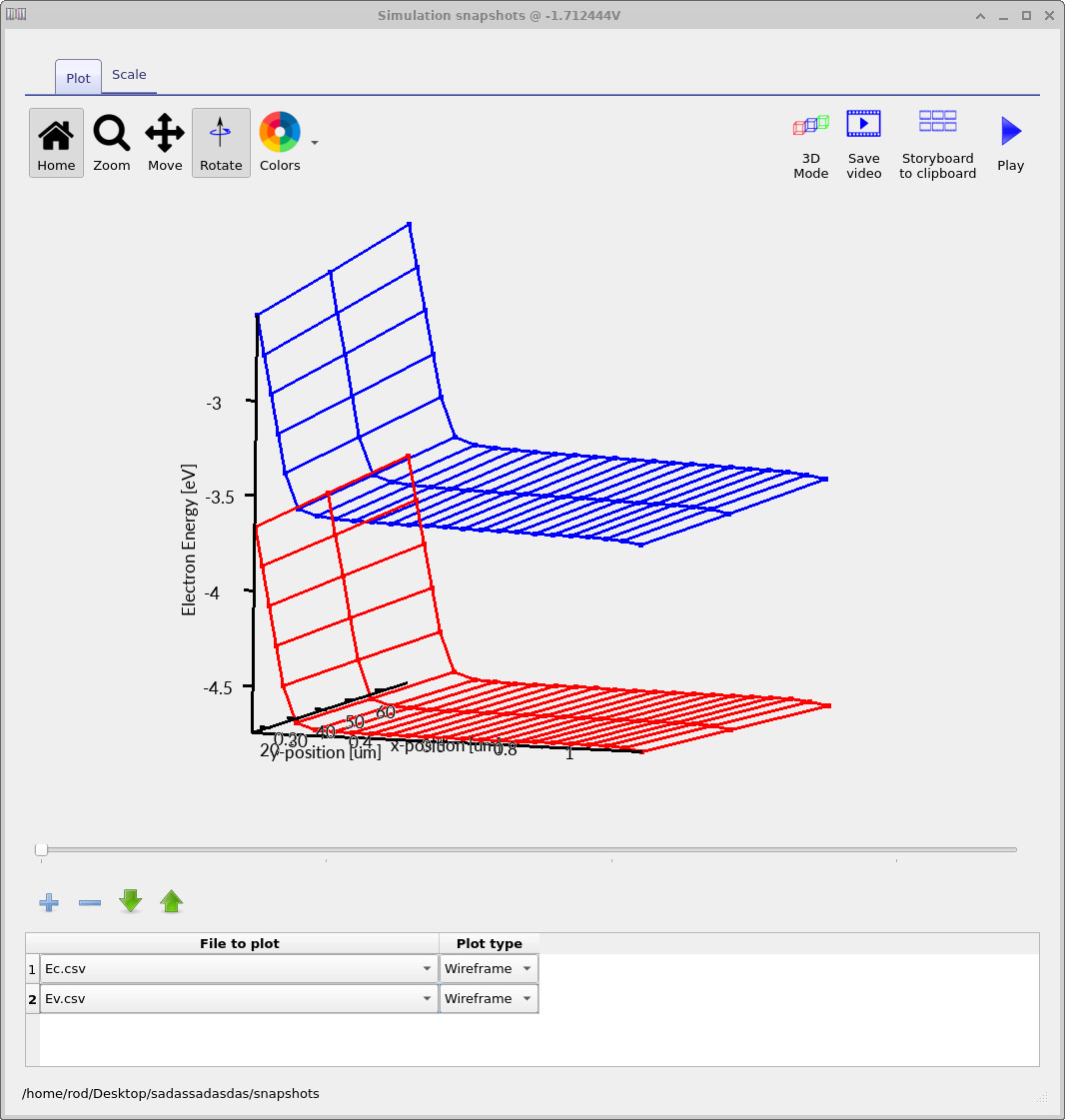

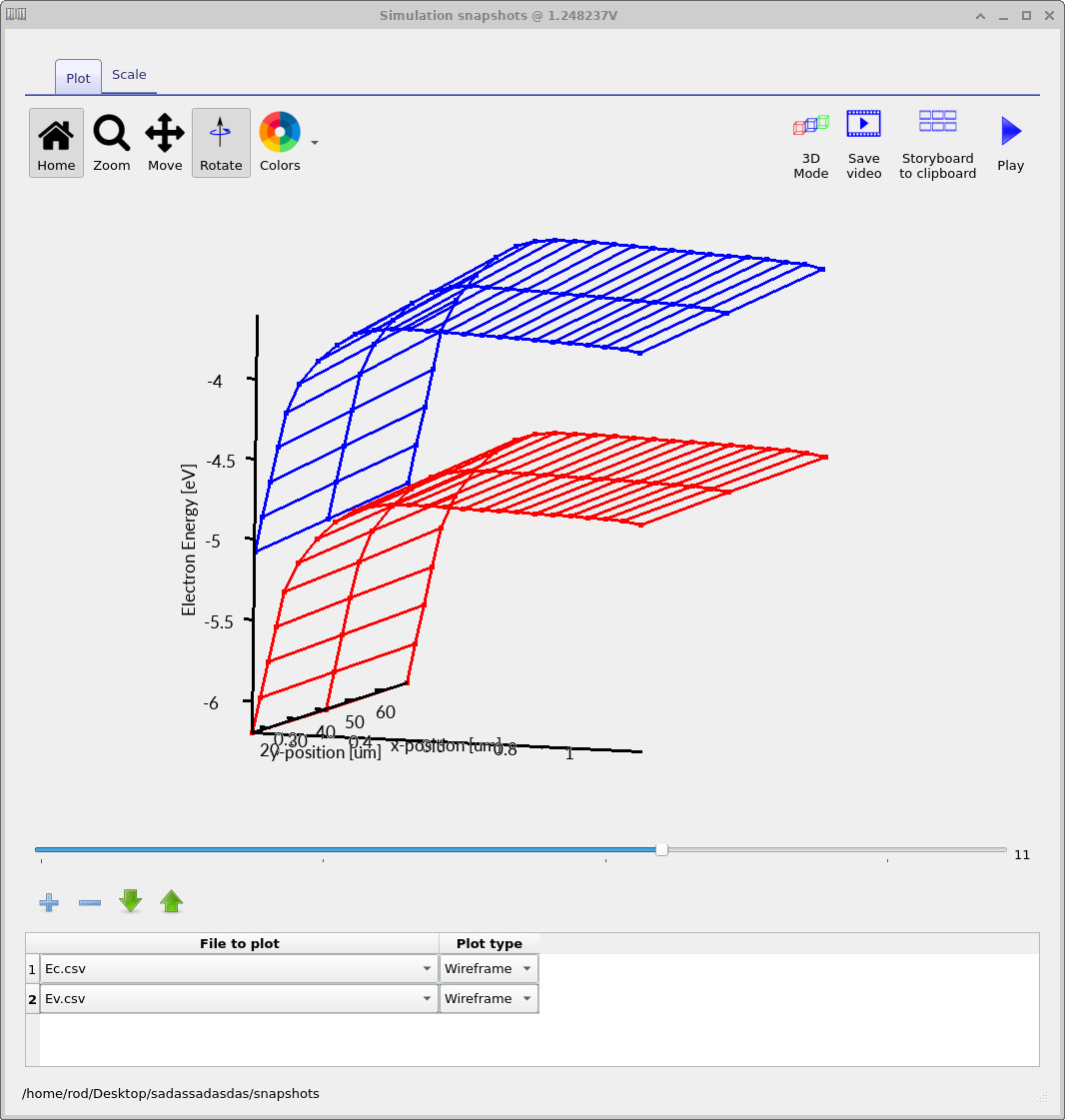

3. 导带和价带弯曲

现在我们检查不同外加栅压下,导带

(Ec.csv)和价带(Ev.csv)随位置的分布。

将它们一起绘制后,

可以直接可视化硅中的能带弯曲,

这是上一节中分析的静电势的直接结果。

在解读图之前,先回顾一下能带边缘是如何定义的会很有帮助。

在这里使用的 drift–diffusion 形式中,导带和价带能量

与静电势 phi 的关系为

Ec(x) = −χ − q φ(x)

以及

Ev(x) = −χ − Eg − q φ(x)

其中 χ 是电子亲和势,Eg 是带隙,

而 φ(x) 是静电势。

由于两个带边都线性依赖于 phi,

因此静电势的任何空间变化都会直接表现为导带和价带的弯曲。

能带边缘通过 snapshots 输出进行可视化。

像之前一样,从 Output 选项卡打开 snapshots 查看器,

然后点击蓝色加号图标两次,添加两个绘图条目。

第一个选择 Ec.csv,第二个选择 Ev.csv。

这样就可以在三维中同时查看导带和价带边缘,

作为位置和外加栅压的函数。

在负栅极偏压下,导带和价带在 Si/SiO2 界面附近都会 向上弯曲。 由于带边跟随静电势变化, 这种向上弯曲反映出相对于体区而言, 表面电势升高。 仅从能带分布本身, 我们就可以推断表面区域被驱动到 一个富空穴的静电构型。

随着栅压变为正值, 界面附近的能带会 向下弯曲。 这种曲率变化表明表面电势降低, 并在硅中形成一个耗尽区。 在这一阶段,NMOS 电容在静电上已经进入耗尽态, 但尚未进入反型。 得出这一结论并不需要对载流子密度作任何假设—— 能带弯曲本身已经直接编码了底层静电学。

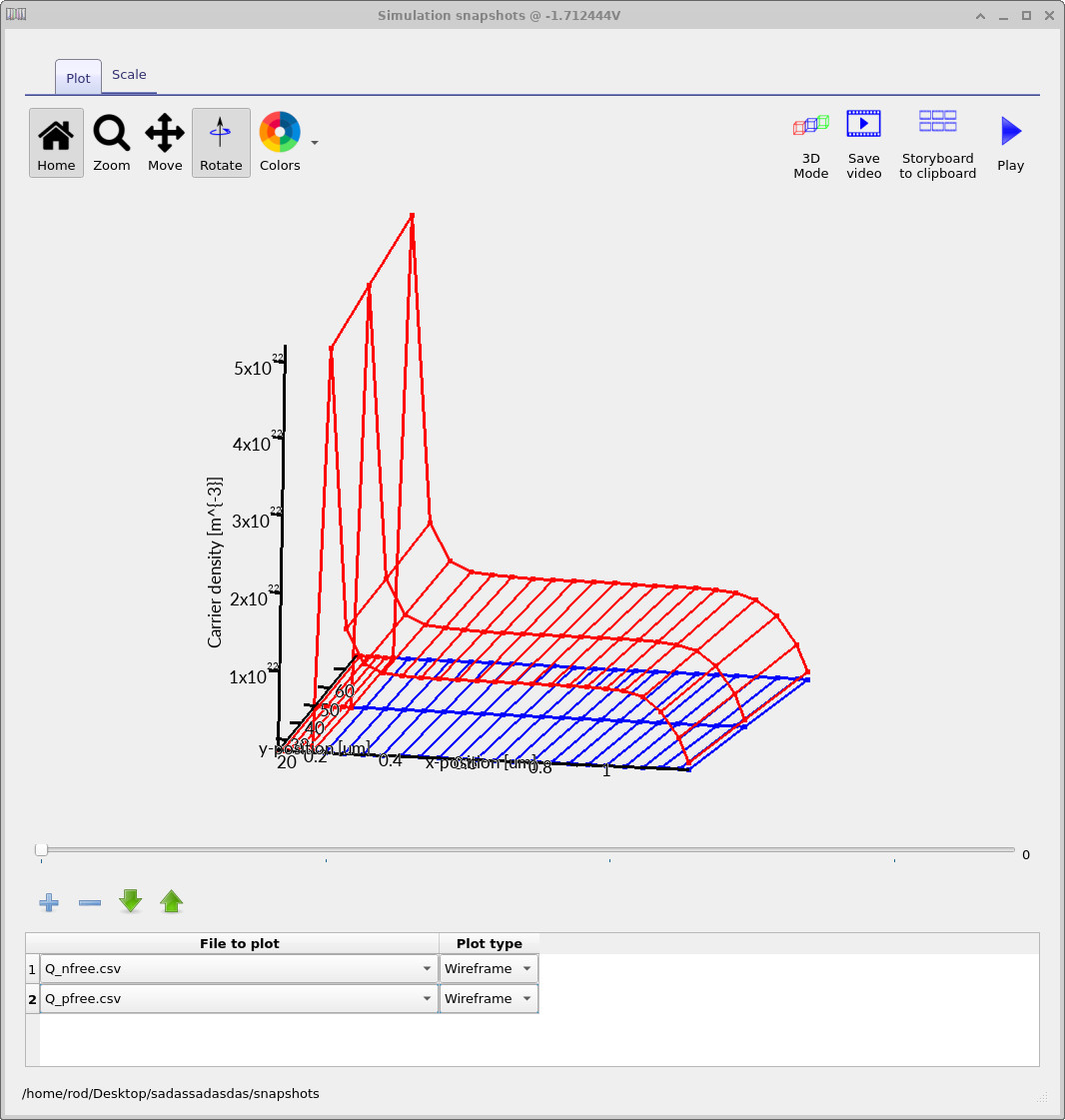

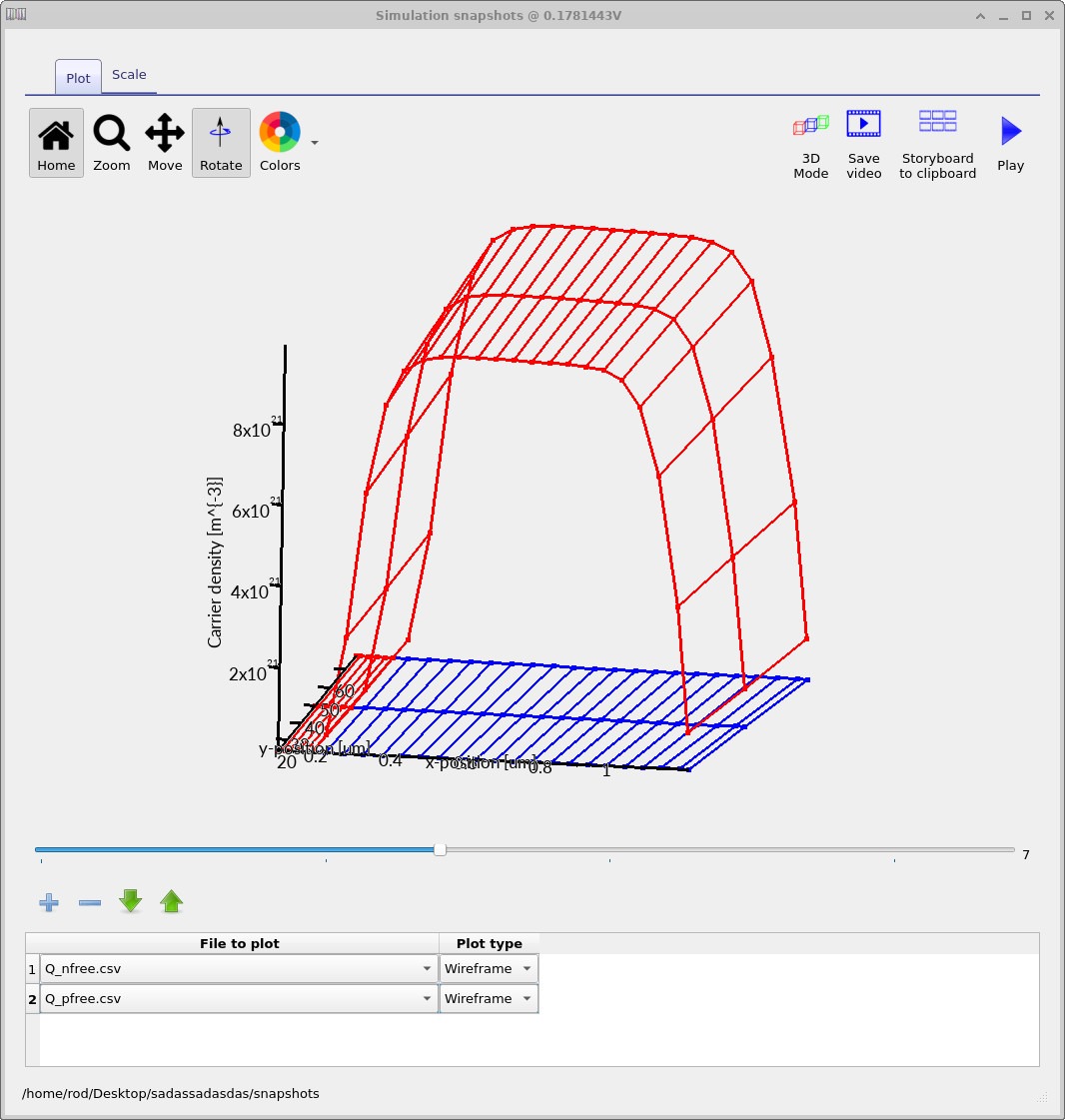

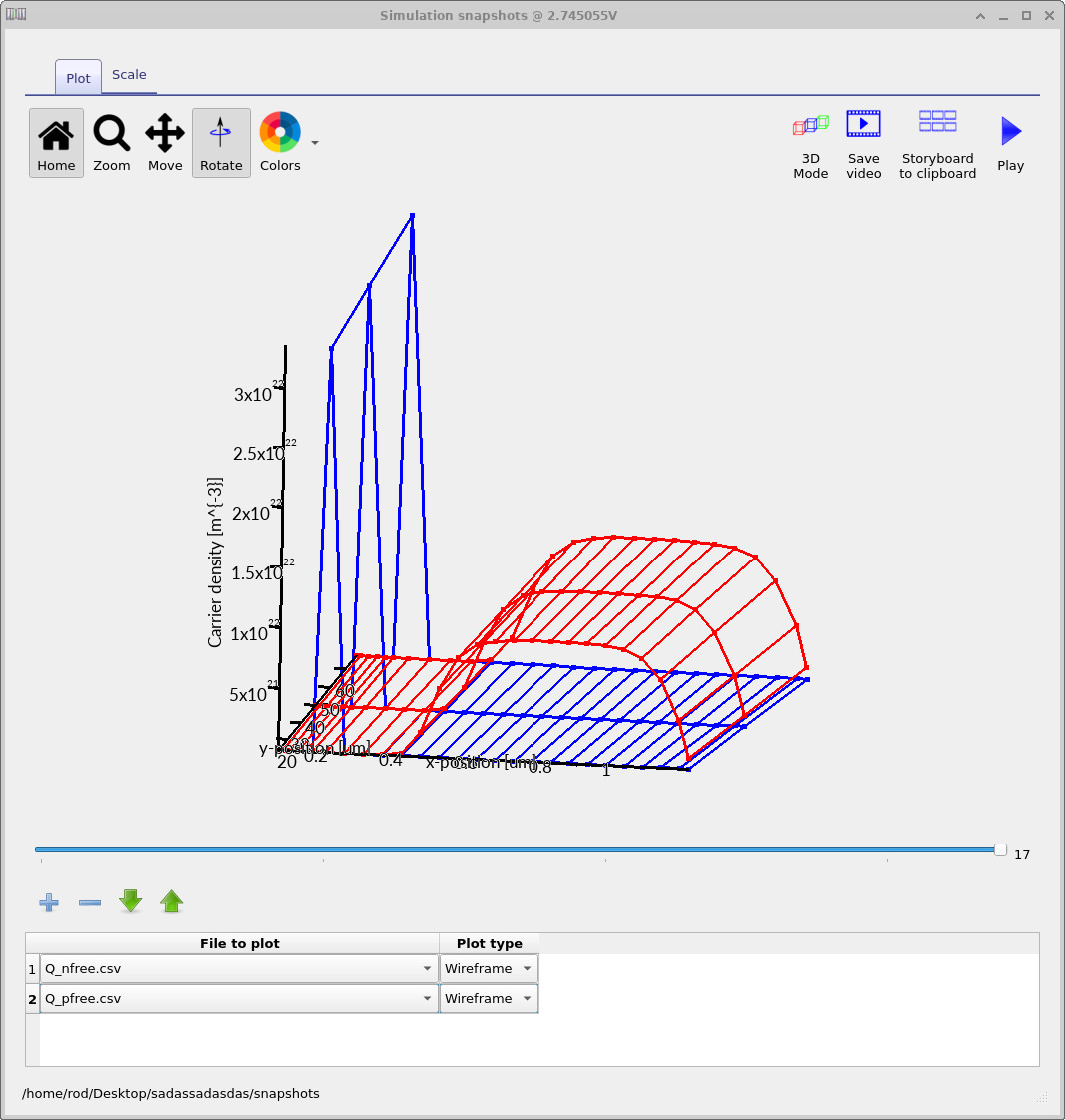

4. 自由载流子密度

现在我们通过检查硅中的自由载流子密度,

来将 NMOS 电容的静电响应具体化。

图 ??–

??

显示了从 snapshots 输出中提取的

空穴密度(Q_pfree.csv)和电子密度(Q_nfree.csv),

对应于代表性的栅极电压。

在 snapshots 查看器中,颜色分配完全由绘图顺序决定:

第一个添加的量会显示为蓝色,

而第二个会显示为红色。

在这里所示的图中,电子(Q_nfree.csv)先被绘制,

因此显示为蓝色;空穴(Q_pfree.csv)后被绘制,

因此显示为红色。

如果以相反顺序添加这些文件,则颜色会反过来。

在负栅极偏压下 (图 ??), 红色曲面对应空穴密度。 在 Si/SiO2 界面处可以看到明显增大, 表明空穴在静电作用下发生了积累。 蓝色曲面(电子密度)在整个硅中都可以忽略不计, 这与负偏压下的 p 型衬底一致。随着栅压增加并接近零 (图 ??), 界面附近的红色曲面幅度下降。 空穴被从表面排斥开, 从而形成一个可移动电荷减少的区域。 这标志着耗尽开始出现, 在这个区域中,空间电荷越来越由固定的电离受主而不是自由载流子主导。

在正栅极偏压下 (图 ??), 界面附近的空穴密度(红色)被强烈抑制, 从而定义出一个清晰的耗尽区。 电子密度(蓝色)在这一偏压范围内仍然较低, 表明器件尚未进入强反型。

综合起来看,这些载流子密度图为之前根据电势和带边图所推断的静电图景 提供了直接且定量的确认。 它们明确显示了积累和耗尽如何由硅中可移动电荷的重新分布产生。 至于强反型——即电子主导表面电荷的情况—— 将留待后续教程介绍。

5. Fermi 能级和能带占据

现在我们通过绘制

导带(Ec.csv)、价带(Ev.csv)以及电子和空穴

准 Fermi 能级(Fn.csv 和 Fp.csv),

将能带和载流子统计联系起来,这些数据都来自 snapshots 输出。

这些量共同描述的不仅是 NMOS 电容的静电学,

还包括在偏压下载流子如何占据可用态。

要重现

??

中所示的图,

打开 Output 选项卡,双击 snapshots 目录,

并使用蓝色加号图标添加四个绘图条目。

按以下顺序选择:

Fn.csv— 电子准 Fermi 能级Fp.csv— 空穴准 Fermi 能级Ec.csv— 导带边缘Ev.csv— 价带边缘

snapshots 查看器根据绘图顺序分配颜色: 第一个量是蓝色, 第二个是红色, 后续条目依次类推。 在这里所示的图中,准 Fermi 能级显示在能带上方, 电子和空穴通过颜色清楚地区分开来。 如果你改变添加文件的顺序,颜色也会相应改变。

使用 snapshots 窗口底部的滑动条在整个电压扫描范围内移动。 这可以让你连续跟踪能带边缘和准 Fermi 能级 如何随外加栅极偏压演化。

从物理上看,这正是 NMOS 电容中预期会出现的行为。 结构中没有源–漏通道,也没有 DC 电流流过。 因此,电子和空穴准 Fermi 能级在整个器件中始终非常接近, 并且几乎保持平坦。 出现的任何微小分离都只是有限偏压步进带来的数值伪影, 并不代表持续的载流子输运。

因此,前面观察到的能带弯曲完全由 静电学驱动: 栅极电压改变静电势, 而后者根据下式移动带边

Ec(x) = −q φ(x) − χ and Ev(x) = Ec(x) − Eg

其中 φ 是静电势,χ 是电子亲和势,而 Eg 是带隙。 准 Fermi 能级仅仅表示这些能带在局部是如何被占据的; 在纯静电的 MOS 电容中,它们不会彼此分离。

💡 要点总结:

在本教程中,你已经看到了相同的物理过程以几种互补方式呈现:

静电势、能带弯曲、载流子密度以及 Fermi 能级。

它们都在描述同一个底层过程——

电荷响应于栅控电场而发生重新分布。

🧪 自己试试看:

在保持器件几何不变的情况下,

使用相同的 NMOS 电容结构探索静电学对材料和偏压参数变化的响应。

- 改变 SiO2 介电常数, 并观察在相同栅压下硅中的电势降 和能带弯曲如何变化。

- 修改衬底掺杂浓度, 并比较耗尽宽度 以及能带边缘的曲率。

- 扩展栅压扫描范围, 并跟踪 φ、Ec、Ev 以及载流子密度如何共同演化。

- 在硅层中切换 Maxwell–Boltzmann 和 Fermi–Dirac 统计, 并比较界面附近的载流子密度。

预期结果

- 提高氧化层介电常数会增强电容耦合, 使更多外加电压分配到硅中。

- 更高的 p 型掺杂会产生更窄的耗尽区; 更轻的掺杂会产生更宽的耗尽区和更平缓的能带弯曲。

- 扩大偏压范围会增加能带弯曲, 但在电容几何中, 它本身不会使准 Fermi 能级彼此分离。

- Fermi–Dirac 统计会抑制高密度下界面附近 不物理的载流子过度占据。