パートA: クイックスタート – 最初のOFETをシミュレーションする

このセクションでは、有機電界効果トランジスタ(OFET)の基本理論を紹介し、その後OghmaNanoを用いたシミュレーション方法を案内します。

1. p型有機電界効果トランジスタ(OFET)の基本理論

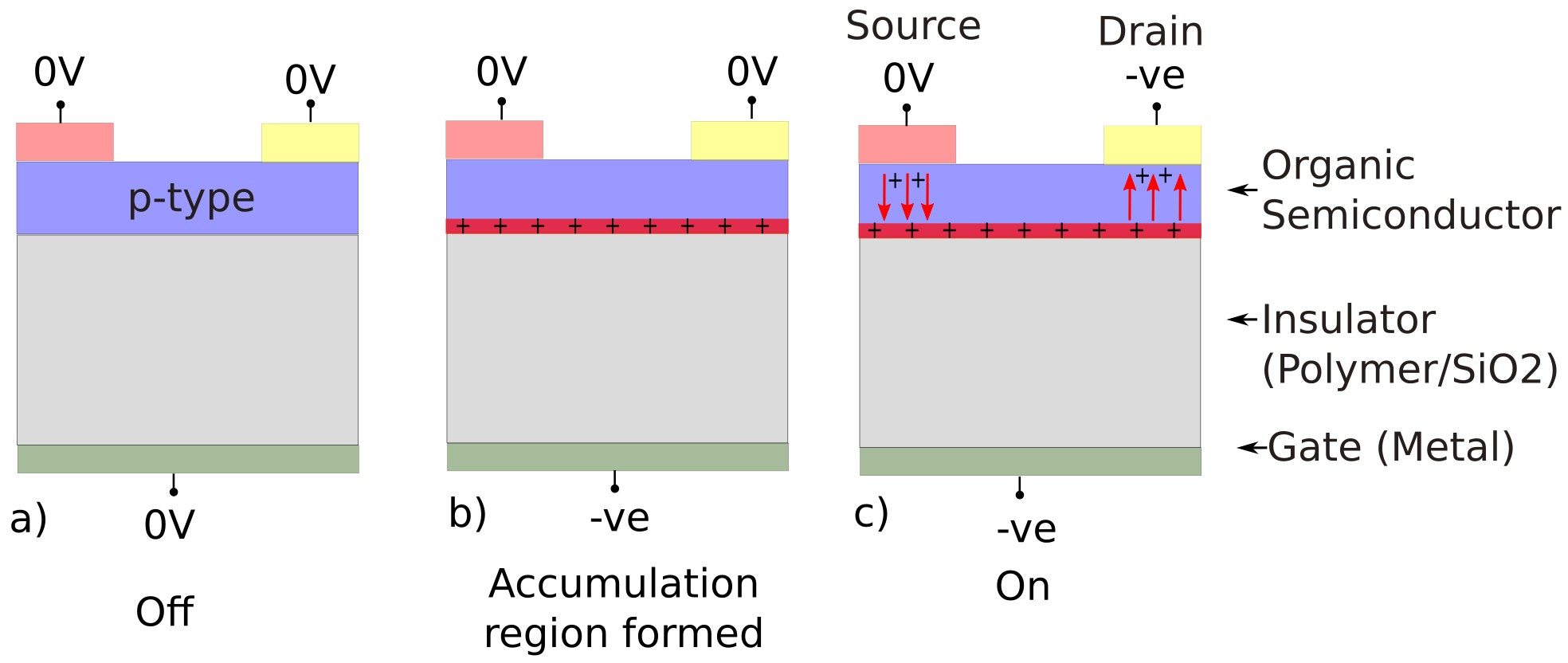

?? は典型的なOFETの構造を示しています。薄い有機半導体層(青)が絶縁性ポリマー/SiO2 層(灰色)の上に堆積されています。2つのコンタクト、Source と Drain は半導体上部に配置され、電荷キャリアの注入と収集を行い、一方で3つ目のコンタクトである Gate(緑)は絶縁体の下に配置され、デバイス動作を制御します。

動作時には、Gate 電極が有機半導体層を介した Source と Drain 間の電荷キャリアの流れを変調します。Gate に電圧を印加すると絶縁体を横切る電場が生じ、これにより半導体–絶縁体界面(赤)に薄い電荷層が形成されます。これは、コンデンサに電位を印加したときに形成される電荷層と非常によく似ています。材料系に応じて、支配的なキャリアは正孔(p型)または電子(n型)になります。p型材料では、正孔層を形成するために負の電位がゲートに印加されます(これは ??b に見ることができます)。Source と Drain の間にバイアスが印加されると、これらのキャリアは誘起されたチャネルを通ってドリフトし、デバイスはオンになります(??c)。ゲートに印加された電圧をオフにすると、電荷チャネルは消失し、Source と Drain 間の電荷キャリアの流れは停止します。一般に、電流レベルは Gate 電圧によって支配されます。あるしきい値以下ではチャネルは絶縁状態のままであり、それを超えるとチャネル伝導度は Gate バイアスとともに増加します。この電界効果制御により、OFET はスイッチとして、あるいは線形領域では増幅器として動作でき、その性能はキャリア移動度、しきい値電圧、コンタクト抵抗などの因子によって決まります。

OFETの動作は ??a–c に示されています:

- 初期状態 — オフ(??a)。 すべての端子が0 Vでは、半導体–絶縁体界面に電荷は誘起されません。 Source と Drain の間に導電路は存在せず、デバイスはオフのままです。

-

Gate バイアス - チャネル形成(??b)。

Gate に 負の 電圧を印加すると、絶縁体を横切る電場が生じます。

この電場は半導体–絶縁体界面へ 正孔 を静電的に引き寄せ、

薄い 蓄積層(チャネル)を形成します。

VDS=0ではデバイスは まだ電流を流しませんが、導電チャネルは形成されています。 -

Drain バイアス - 電流の流れ(??c)。

Source に対して 負の Drain 電圧を印加すると

(

VDS<0, Source ≈ 0 V)、 Source からチャネルへ正孔が注入されます。 正孔は Gate によって誘起されたチャネルに沿って Drain 方向へドリフトし、 Drain 電流を生じます。より負の Gate バイアスは蓄積チャネルを強め、電流を増加させます。

要するに、ゲートの電場は半導体–絶縁体界面に導電チャネルを 誘起 します。このチャネルが存在するときのみ source と drain の間に電流が流れ、 これにより OFET は電圧制御スイッチまたは増幅器として動作できます。ゲートバイアスを除去するとチャネルは空乏化し、デバイスはオフになります。

上の説明は、正孔が多数キャリアである p型 OFET を示しています。OFET は、電子が導電チャネルを形成する n型デバイス(この場合はゲートに正の電圧が印加されます)や、印加バイアスに応じて正孔と電子の両方を輸送できる両極性デバイスとしても動作できます。3つすべての動作モードが可能ですが、有機半導体における正孔輸送は通常、周囲環境条件下でより安定であり、実験的にも実現しやすいため、p型 OFET が依然として最も一般的です。

2. クイックスタート OFET シミュレーション

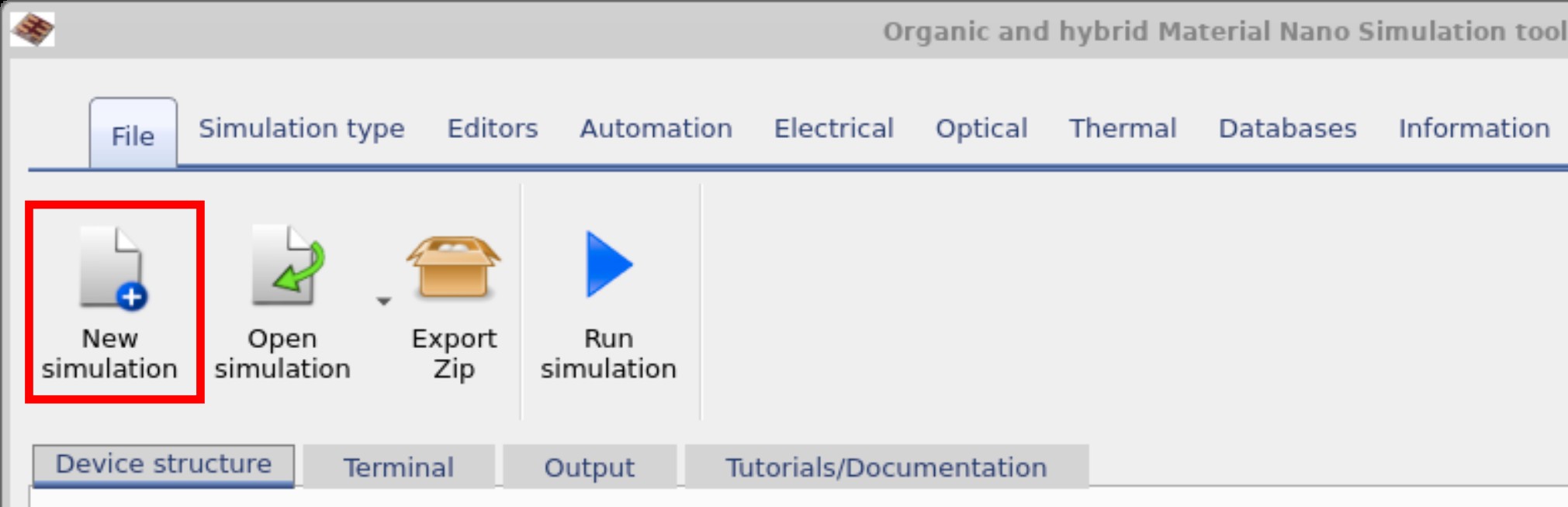

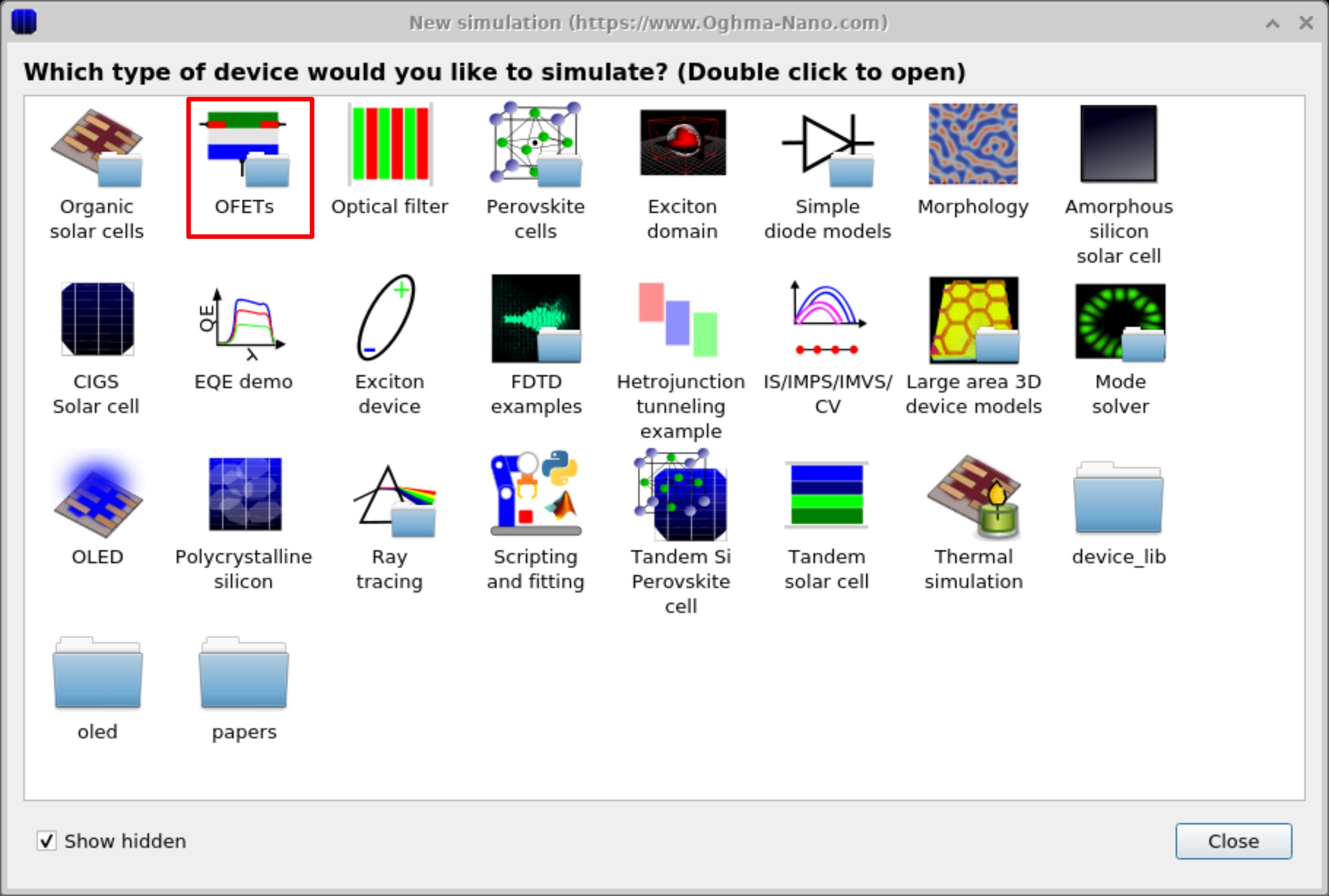

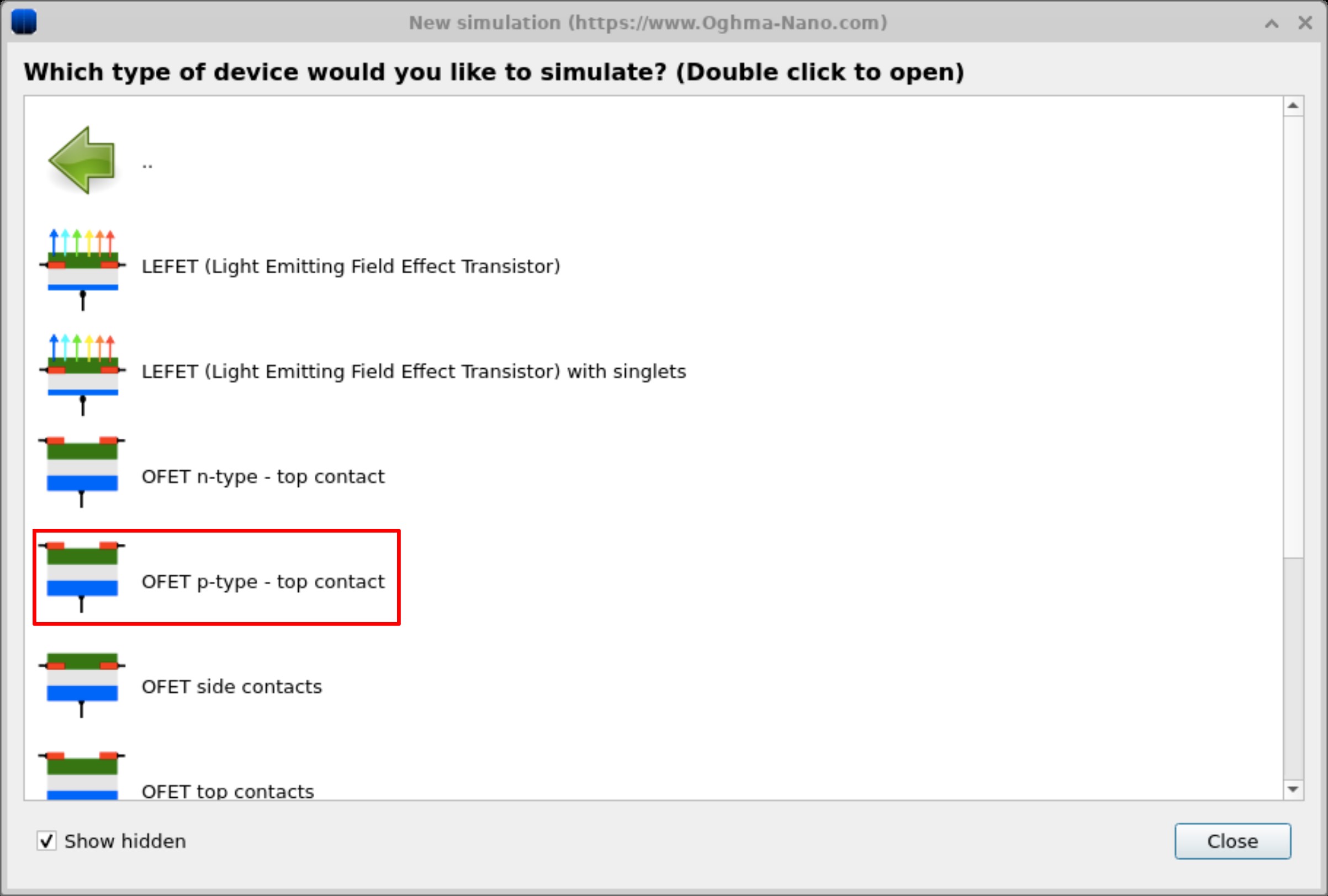

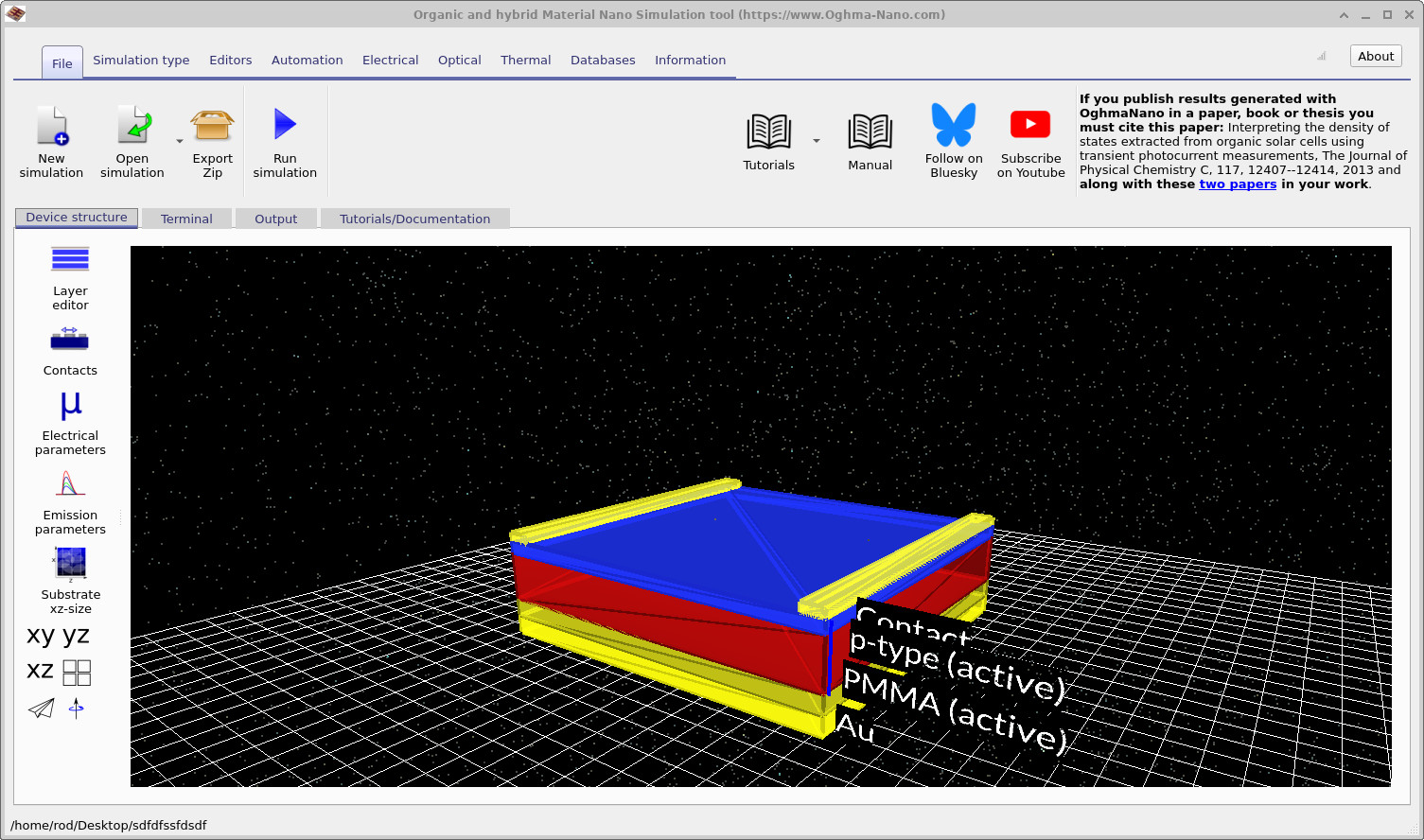

このチュートリアルでは、トップコンタクトを持つ p型 MOSFET に焦点を当てます。p型半導体は、一般により高い 正孔移動度 を示すため、 有機電子デバイスで最も広く用いられています。新しい OFET シミュレーションを作成するには、OghmaNano メインウィンドウの New simulation ボタンをクリックします(??)。次に、新規シミュレーションウィンドウで OFET simulations をダブルクリックします(?? を参照)。これにより OFET のサブメニューが開き、そこには他の 種類の OFET も保存されています。この例では "OFET p-type top contact" を使用します(??)。これをダブルクリックし、新しいシミュレーションをディスクに保存してください。

新しいシミュレーションを保存すると、?? のようなウィンドウが表示されるはずです。黒い背景上で左マウスボタンをクリックしたままドラッグすると、シミュレーションウィンドウを回転させてデバイスを3Dで表示できます。このデバイスには、gate、source、drain の3つのコンタクトがあることがわかります。source と drain はシミュレーション上部の金色のバーとして表示され、半導体層は青、絶縁層は赤で表示されます。gate コンタクトは構造の下部に見えます。

3. 最初の OFET シミュレーションを実行する

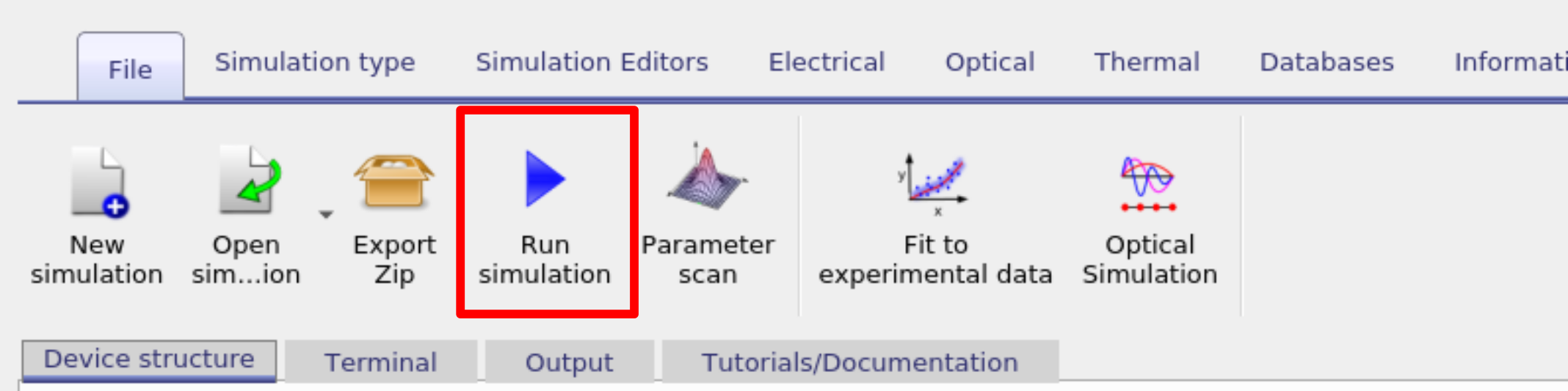

シミュレーションを開始するには、Play ボタンをクリックします。1D シミュレーションと比較して、2D シミュレーションは通常より長い時間がかかります。これは、ソルバーが増加したメッシュ点数を持つメッシュを処理しなければならないためです。トラップが有効になっている場合、キャリアの捕獲/脱出方程式も各メッシュ点で解かれるため、計算負荷はさらに増加します。一般に、問題の次元を上げると、実行時間とメモリ要求は急速に増加します。

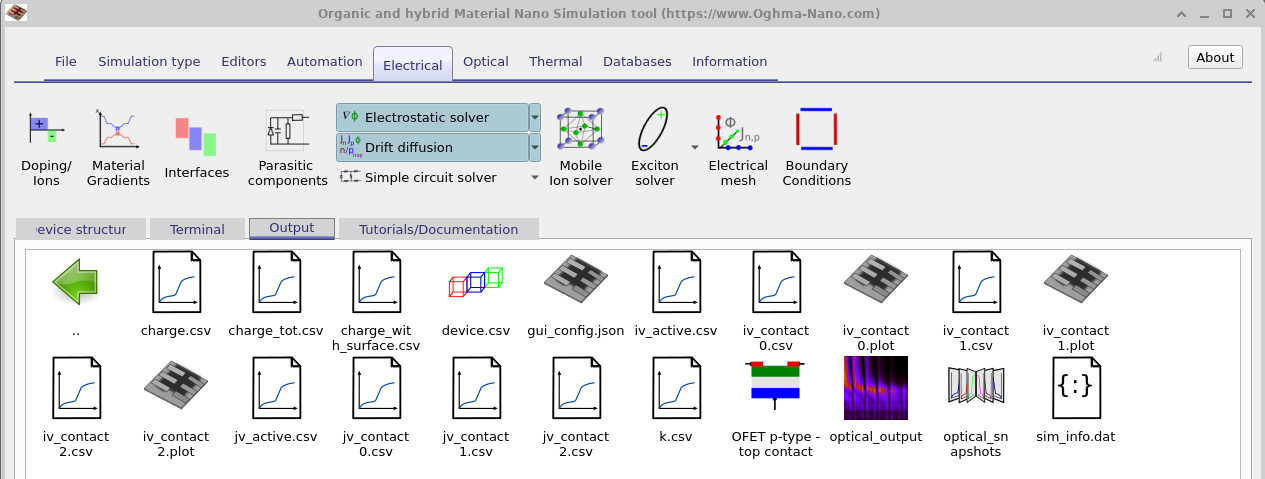

jv_contact_0.csv, jv_contact_1.csv, jv_contact_2.csv)、

charge.csv、device.csv、sim_info.dat などの

要約および診断ファイルも併せて生成されます。

シミュレーションが終了したら、Output タブを開きます。OFET には複数のコンタクトがあるため、1D の場合より多くのファイルが表示されます。これは、各コンタクトごとに JV 曲線が生成され、それぞれの曲線がそのコンタクトを通ってデバイスへ流入または流出する電流を表しているためです。生成されるファイルの要約を以下に示します。

| ファイル名 | 説明 |

|---|---|

| contact_iv0.dat | コンタクト 0 の電流 vs 電圧曲線 |

| contact_iv1.dat | コンタクト 1 の電流 vs 電圧曲線 |

| contact_iv2.dat | コンタクト 2 の電流 vs 電圧曲線 |

| contact_jv0.dat | コンタクト 0 の電流密度 vs 電圧曲線 |

| contact_jv1.dat | コンタクト 1 の電流密度 vs 電圧曲線 |

| contact_jv2.dat | コンタクト 2 の電流密度 vs 電圧曲線 |

| snapshots/ | シミュレーションスナップショット |

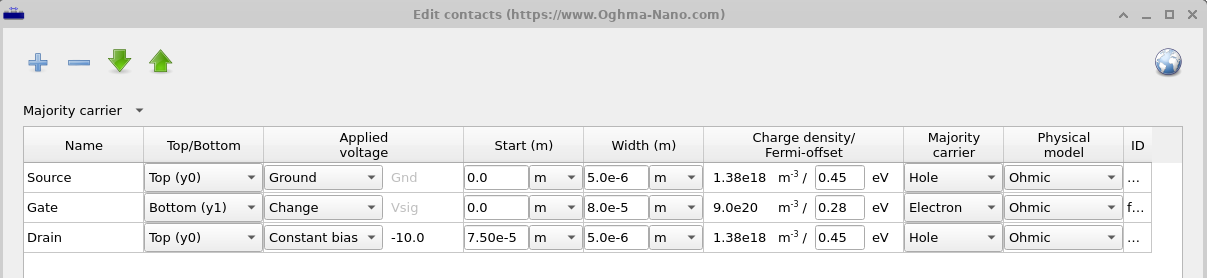

jv_contact_0.csv、jb_contact_1.csv、jb_contact_2.csv の各ファイルをダブルクリックして、それぞれのコンタクトの曲線を確認してください。OghmaNano におけるコンタクトは、contact editor で定義された順序で 0 から N までラベル付けされます(図

?? を参照)。したがって、この場合 Contact 0 が source、contact 1 が gate、contact 2 が drain になります。contact editor はセクション 3.1.8 で詳しく説明されていますが、これは 2D シミュレーションであるため、さらに2つの列が追加されています。それは start と width です。これらは、x 軸上でのコンタクトの開始位置と、その x 軸方向の幅を定義します。source は \(0~m\) から始まり、\(5 \mu m\) まで広がります。drain は \(75~\mu m\) から始まり、\(5 \mu m\) まで広がります。一方、gate は \(0~m\) から始まり、デバイス全幅である \(80~ \mu m\) を覆うように広がります。また、Applied Voltage 列の下で、source は Ground とマークされていることにも注意してください。これは、この接点に 0V が印加されることを意味します。gate は change とマークされており、JV editor で定義された電圧ランプがこのコンタクトに印加されることを意味します。drain は constant bias とマークされ、電圧は 10V です。これは、この接点に 10V の一定電圧が印加されることを意味します。したがって、source と drain の間に一定電圧を印加しながら、gate コンタクトを掃引していることになります。

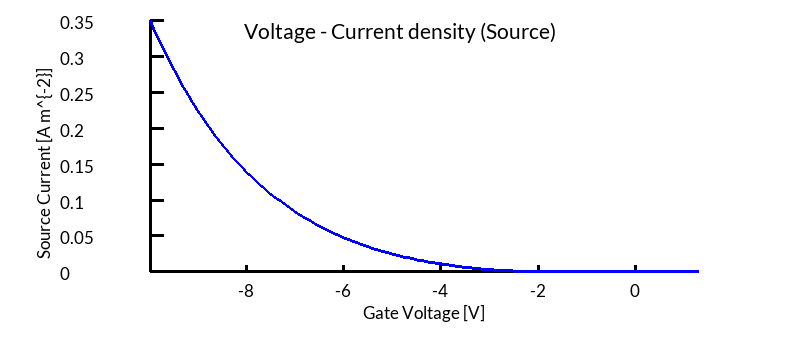

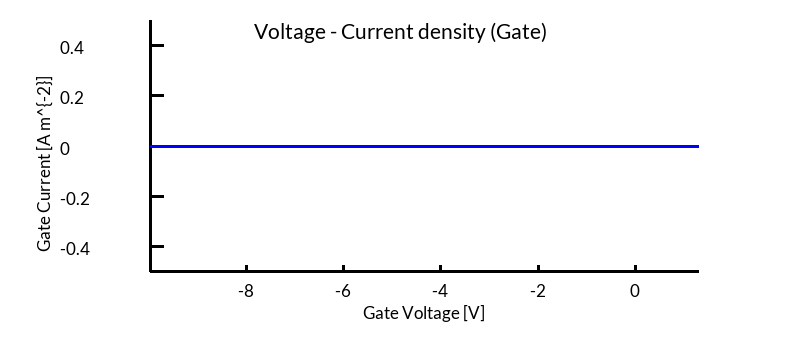

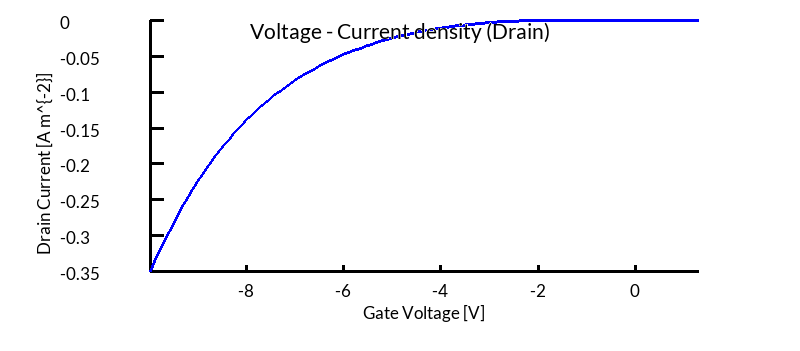

??、 ?? および ?? は、3つの OFET コンタクトそれぞれにおける JV 曲線を示しています。?? と ?? を見ると、ゲート電圧がより負になるにつれて、source と drain における電流もより負になることがわかります。導通可能にするために、チャネルへ正孔を引き寄せるよう負電圧を印加しています。また、Gate に電流が流れていないこともわかります。これは、電流が誘電体によって遮断されているためです。

jv_contact0.csv - source)の JV 曲線。

負符号は、この端子を通して電流がデバイスから流出していることを示します。

jv_contact1.csv - gate)の JV 曲線。

gate は絶縁されているため、電流はゼロ近傍に保たれます。

jv_contact2.csv - drain)の JV 曲線。

正の電流は、電荷注入がデバイス内へ向かっていることに対応します。

👉 次のステップ: それでは パートB に進み、OFET 結果を 2D および 3D で可視化し、電流の流れ、電荷密度、デバイス内部電場をより詳しく調べる方法を学びます。