大面積デバイスシミュレーション – パート B: スキャンの実行と抵抗・電圧損失の解釈

ステップ 1: スキャンシミュレーションを実行する

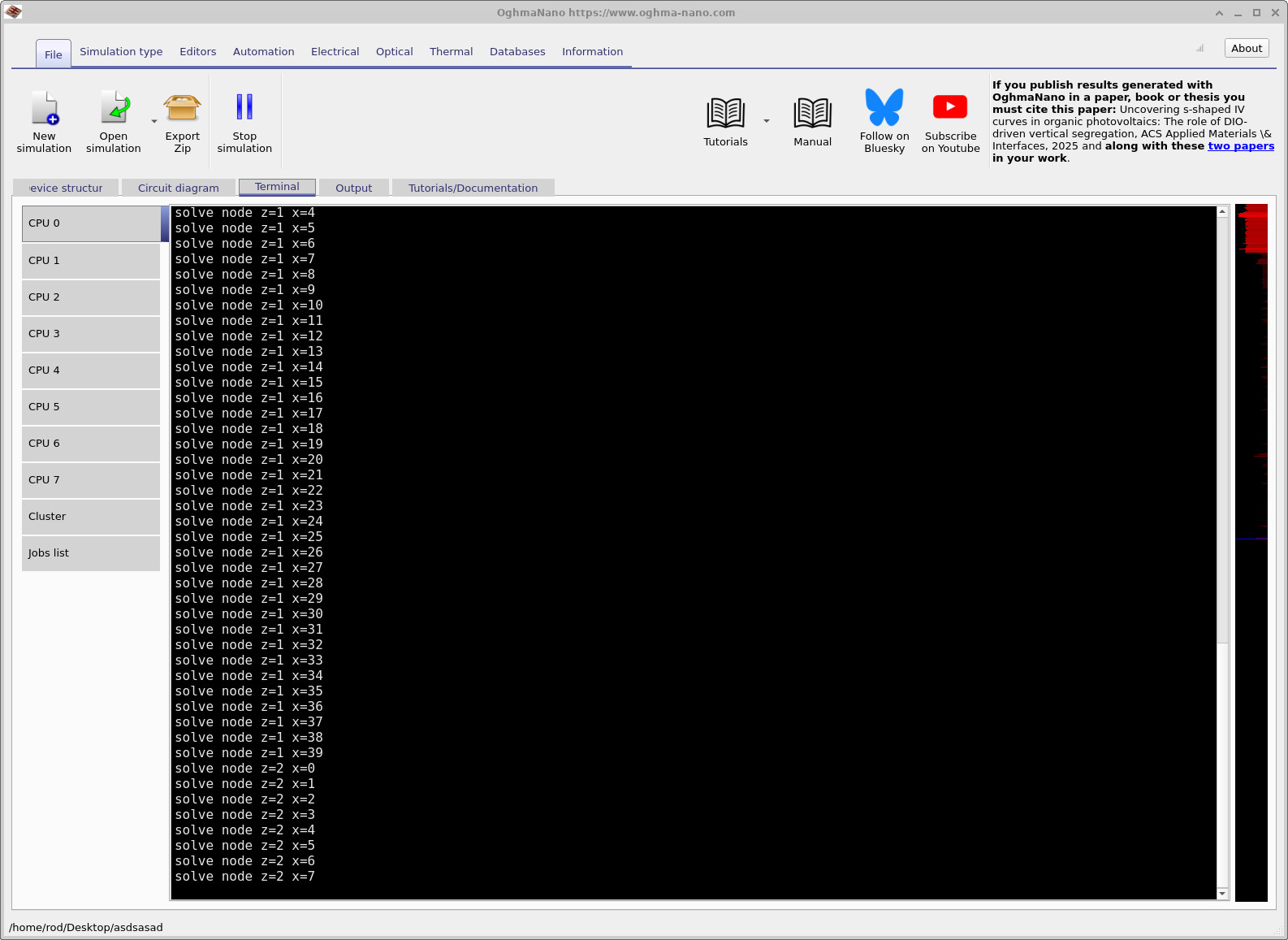

Run simulation(青い三角)をクリックするか、F9 を押してスキャンを開始します。ターミナル出力がストリーム表示され始めます(?? を参照)。

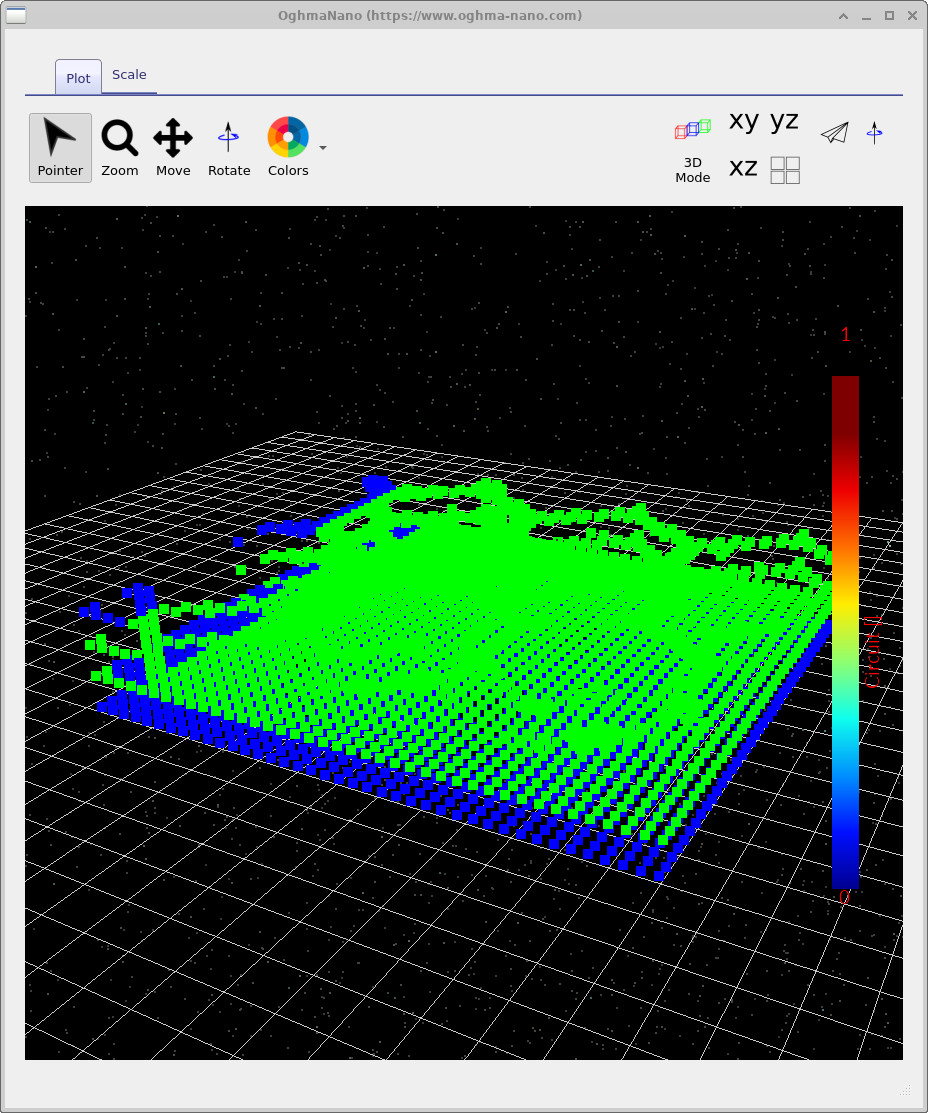

物理的に起きていることは単純です。OghmaNano はコンタクトを 3D 抵抗ネットワークとして扱っています。次に、底面上の 1 つの メッシュ点に電圧励起を加え、回路を解き、上部抽出コンタクトまでの有効抵抗を抽出し、それを次の点に対して繰り返します。

40 × 40 のスキャンでは、これは 40 × 40 = 1600 回の個別の回路計算を意味します。これがスキャンに時間がかかる理由です。単一の JV スイープを実行しているのではなく、空間マップを構築するために多くの小さな DC 計算を実行しているのです。

💡 実用上の注意: スキャン分解能を大幅に上げると、実行時間はおおよそスキャン点数に比例して増加します。高分解能ではよりきれいなマップが得られますが、時間がかかります。

ステップ 2: 電気メッシュを理解する

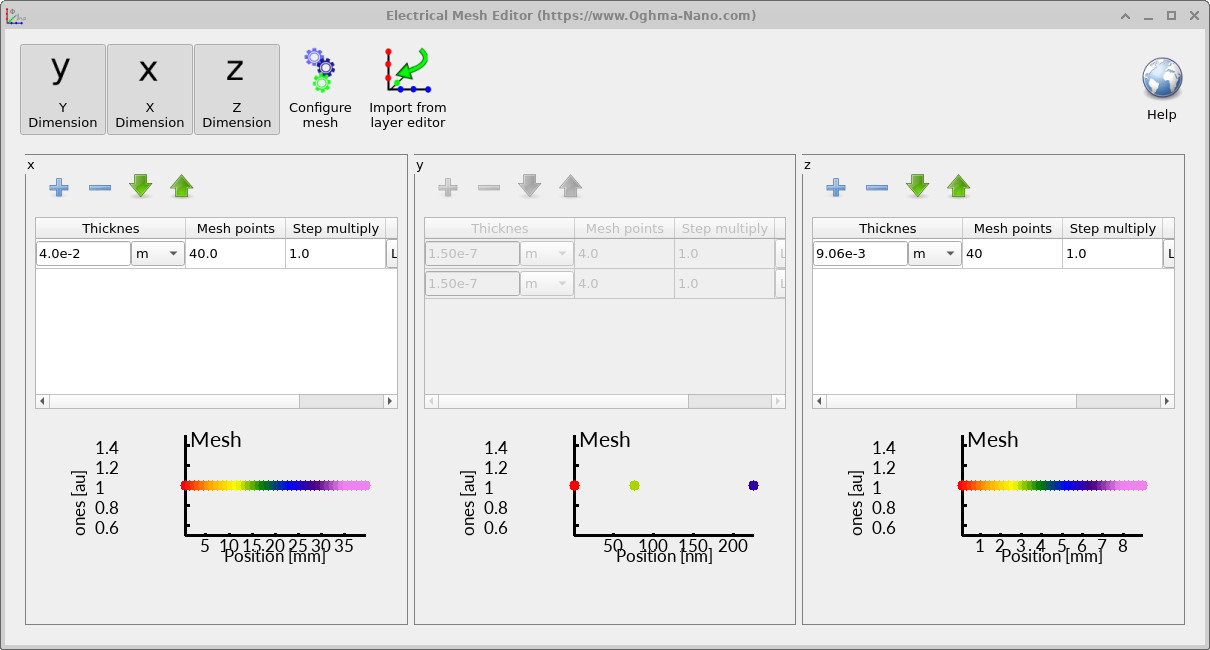

スキャン分解能は、Electrical タブの Electrical mesh で定義される電気メッシュによって制御されます(?? を参照)。この例では、x–z 平面で 40 × 40 点を使用しています。y 方向は層スタックによって設定されます(つまり、ソルバーは定義した層から垂直方向の離散化を把握しています)。

大まかな目安として:

- 点数が少なすぎる → 抵抗マップがブロック状になり、メッシュ周辺の微細な電流集中を見逃す可能性があります。

- 点数が多すぎる → 回路計算回数が増えるため、スキャンが遅くなることがあります。

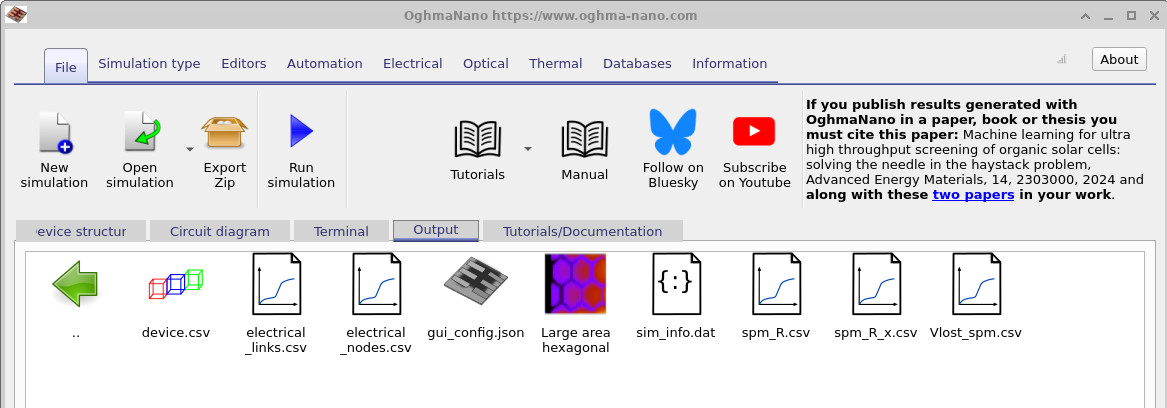

ステップ 3: スキャンによって生成される出力ファイル

スキャンが完了したら、Output タブへ移動します。?? に示すようなファイルが見えるはずです。

spm_R.csv)、そのスライス(spm_R_x.csv)、および電圧損失マップ(Vlost_spm.csv)です。

| ファイル名 | 説明 |

|---|---|

electrical_links.csv | 3D 回路メッシュ内の抵抗リンク(エッジ)の一覧 |

electrical_nodes.csv | 3D メッシュ内の回路ノード(位置と接続性)の一覧 |

spm_R.csv | 走査型プローブ顕微鏡抵抗マップ(位置に対する有効抵抗) |

spm_R_x.csv | デバイス全体の抵抗を示す spm_R.csv の 1D スライス |

Vlost_spm.csv | コンタクト抵抗による各スキャン点での推定電圧損失(ΔV) |

ステップ 4: 抵抗マップとスライスを表示する

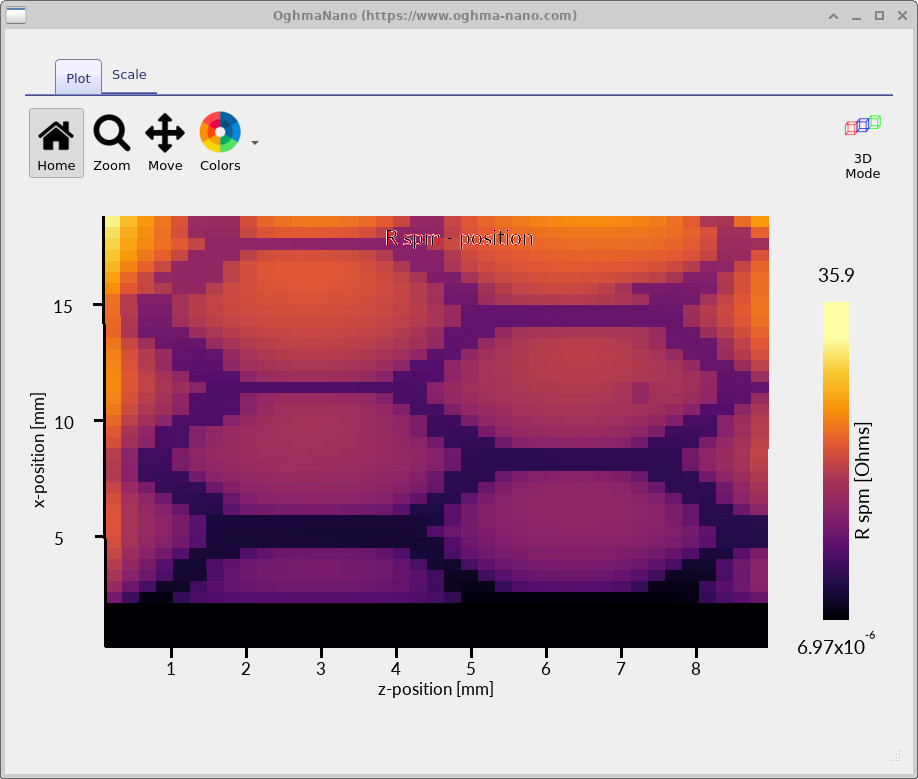

spm_R.csv)。低抵抗は抽出バーおよび

金属メッシュ線付近で生じます。最高抵抗は通常、その両方から離れたセル内部の深い位置に現れます。

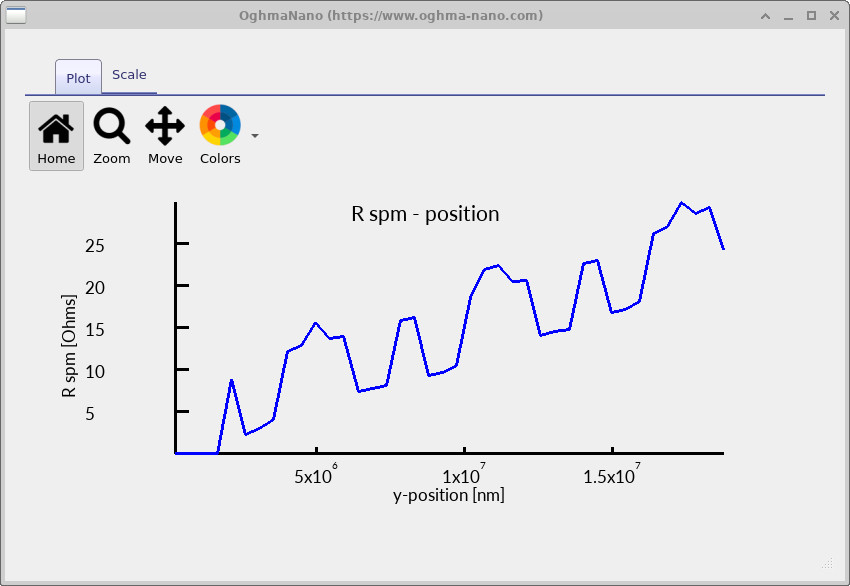

spm_R_x.csv からの抵抗スライス。抵抗は抽出端からの距離とともに増加し、

スライスが金属メッシュセグメントの近くを通る位置では周期的に低下します。

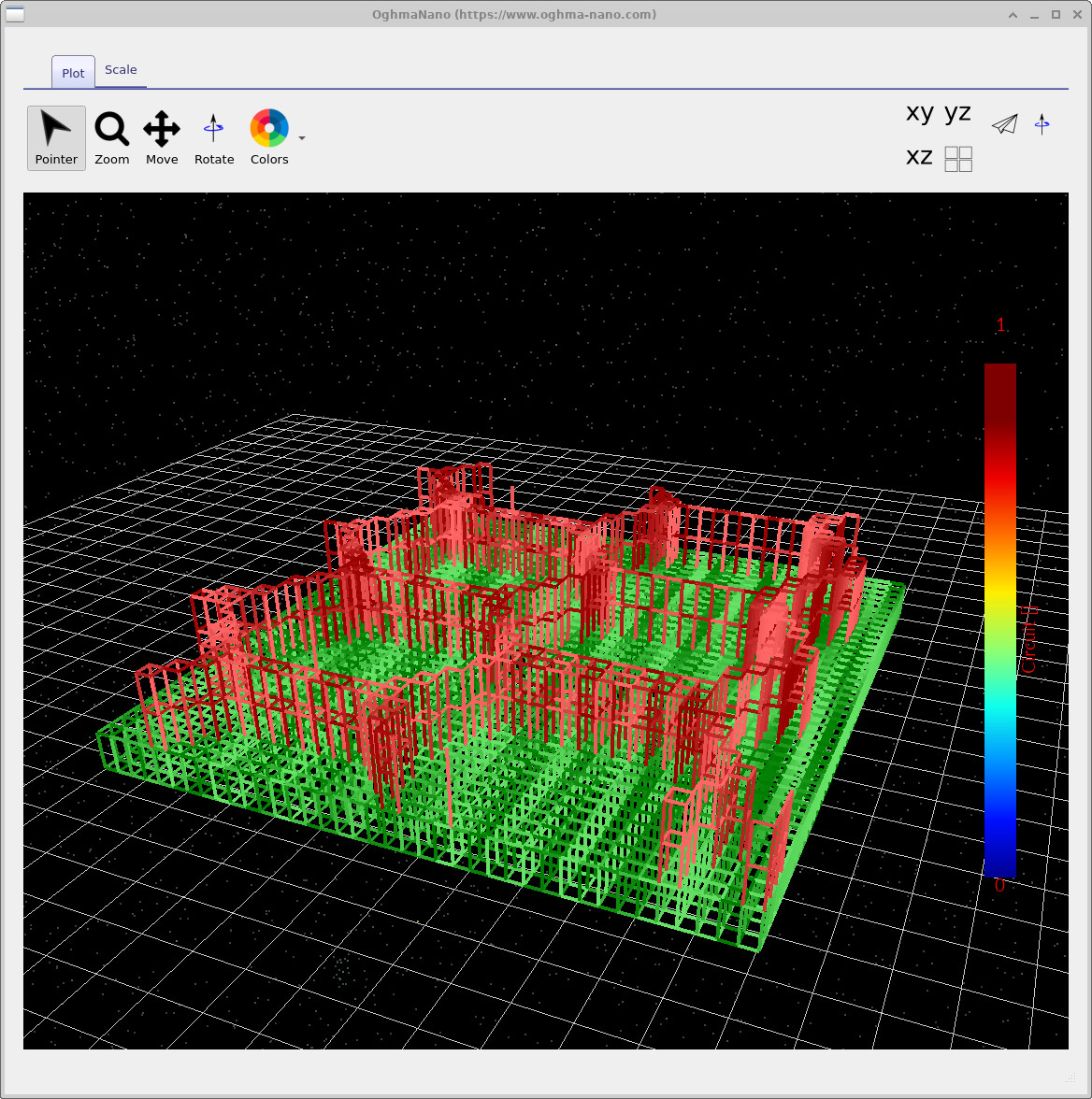

spm_R.csv をダブルクリックして抵抗マップを表示します(?? を参照)。カラースケールは、各底面点と抽出コンタクトとの間の有効抵抗を表しています。

- 抽出コンタクト(プロット中の暗いバー)の近くでは抵抗は低くなります。電流がデバイスから出るまでの経路が短いためです。

- 金属メッシュ線の近くでは抵抗は低くなります。電流が高伝導な金属ネットワークへすばやく入れるためです。

- 最も高い抵抗は、メッシュセルの中心付近で、かつ抽出端から遠い位置に現れる傾向があります。これは、電流がポリマー内を横方向により長い距離移動しなければならないためです。

この例では抵抗値は オーム オーダーであり、印刷コンタクトにおける電流拡散として物理的に妥当なスケールです。しかし、数十オームに近づく値は多くのデバイスにとって無害ではないことに注意してください。活性領域から外部コンタクトまで 30–40 Ω の経路があると、実効フィルファクタ(PV)を大きく低下させたり、輝度不均一(OLED)を引き起こしたりする可能性があります。

spm_R_x.csv をダブルクリックしてマップの 1D スライスを表示します(??)。このプロットは物理を明示的に示します:

- 抽出コンタクトから離れるほど抵抗は増加します(横方向の電流経路が長くなるため)。

- スキャンが金属メッシュ線の上または近くを通るたびに抵抗は低下します(横方向経路が短絡されるため)。

これが重要な診断結果です。これはコンタクトがどれだけ悪いかだけでなく、どこが悪いかも示し、したがってどのような形状または材料変更でそれを改善できるかを教えてくれます。

ステップ 5: 回路メッシュ(リンクとノード)を可視化する

デバッグや解釈のためには、回路表現そのものを可視化すると便利なことがあります。リンクおよびノードの可視化(サンプル出力ではしばしば links.jpg および nodes.jpg として表示されます)をダブルクリックしてください。

これらのコンタクト問題では、回路解釈は文字通りです。各リンクは抵抗であり、各ノードは接点であり、ソルバーはネットワーク全体で Kirchhoff の法則を満たしています。

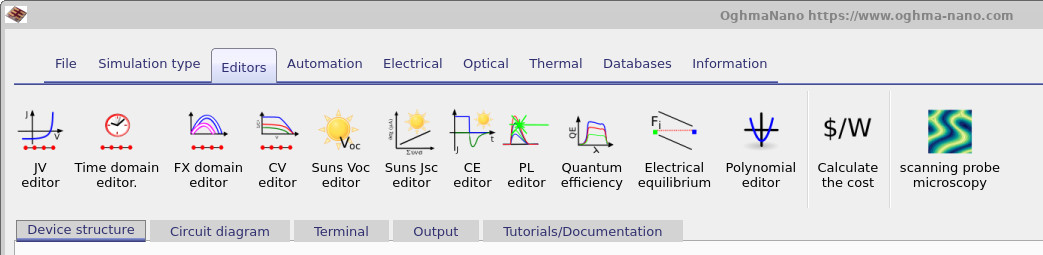

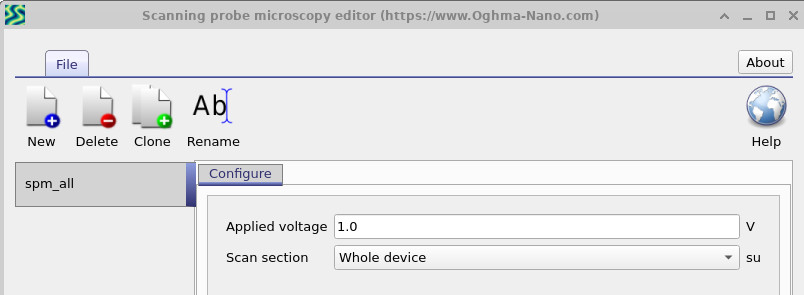

ステップ 6: スキャンを設定する(Scanning Probe Microscopy editor)

今実行したスキャンは、Scanning Probe Microscopy (SPM) editor を使って設定されています。これは editor ribbon から開くことができます(?? を参照)。

設定ウィンドウ(??)では、印加電圧と、スキャンをデバイス全体に対して行うか一部分のみに対して行うかを選べます。特定領域だけに関心がある場合、一部分のみの設定は高速な反復に役立ちます。

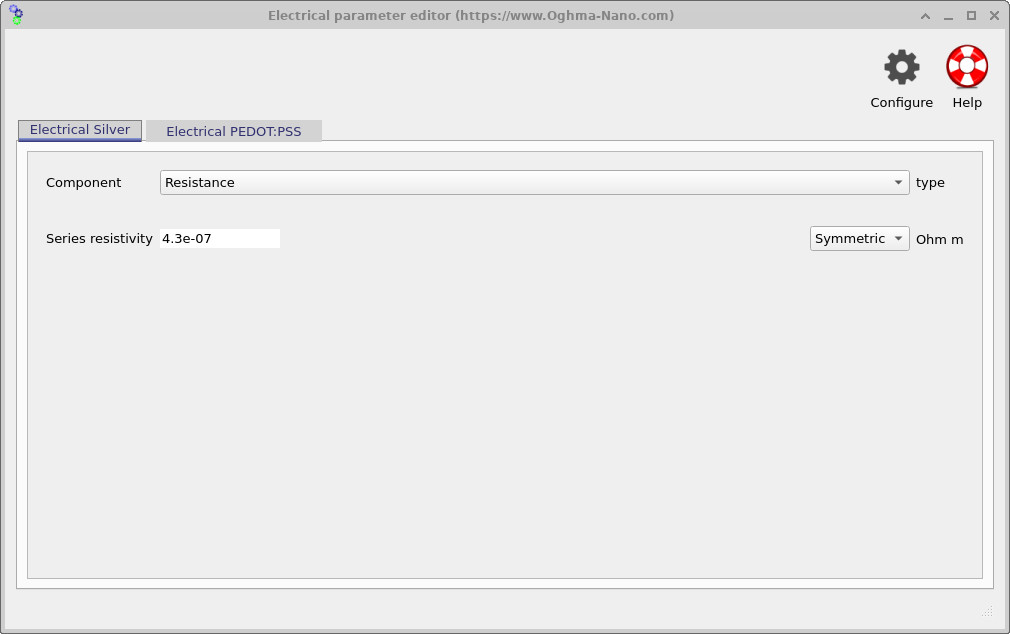

ステップ 7: 材料抵抗率を編集する(そしてそれがなぜ重要か)

設計上のトレードオフを調べるために、各導電層の電気パラメータを編集できます。Device structure タブで Electrical parameters をクリックして electrical parameter editor を開きます(??)。ここでは、自分の材料について測定した抵抗率を入力し、スケールアップされたコンタクトがどのように振る舞うかを即座に予測できます。

この種のパラメトリック探索こそがモデリングの本質です。より良いポリマー、より高密度なメッシュ、あるいは異なる抽出レイアウトのどれが製造前に最大の性能向上をもたらすかを定量化できます。

👉 次のステップ: パート C に進み、コンタクト形状(メッシュピッチ、線幅、抽出レイアウト)を編集して性能を最適化してください。